intJ

8282

r-------,

&-

__

IOQ

:

I

I

I

I I

L

______

_

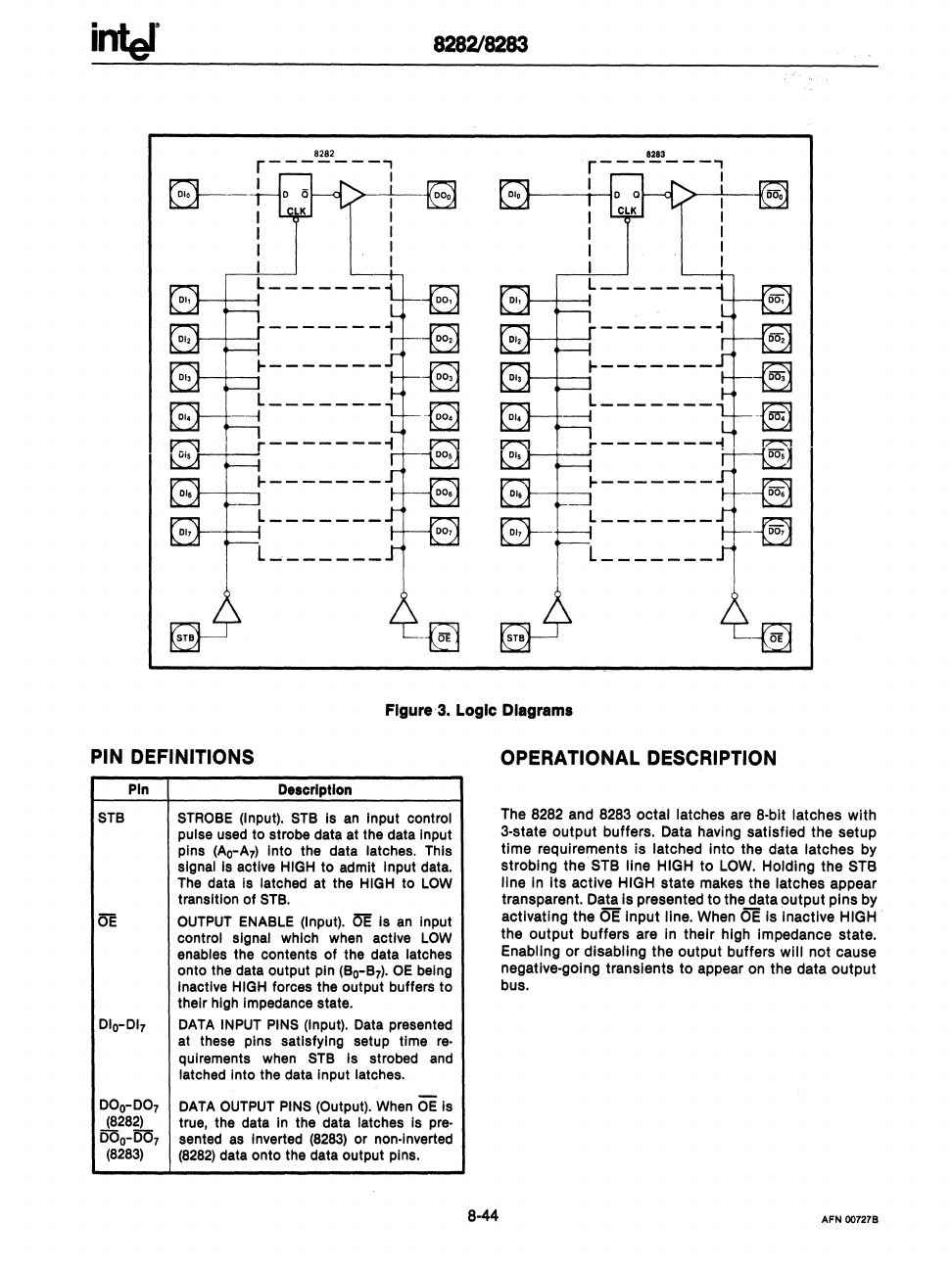

828218283

Figure

3.

Logic Diagrams

L

______

_

PIN DEFINITIONS

OPERATIONAL DESCRIPTION

Pin

STB

OE

01

0-

01

7

00

0

-00

7

(8282)

000-1)(57

(8283)

D.scrlptlon

STROBE

(Input).

STB

Is

an

Input control

pulse

used

to strobe data at the data Input

pins

(Ao-A7)

Into the data latches. This

signal

Is

active

HIGH

to admit Input

data.

The

data

Is

latched at the

HIGH

to

LOW

transition of

STB.

OUTPUT

ENABLE

(Input).

C5"E

Is

an

Input

control signal which

when

active

LOW

enables the contents of the data latches

onto the data output

pin

(Bo-B7).

OE

being

Inactive

HIGH

forces the output buffers to

their high

Impedance

state.

DATA

INPUT

PINS

(Input).

Data

presented

at these pins satisfying setup time

re-

quirements

when

STB

Is strobed

and

latched Into the data Input latches.

DATA

OUTPUT

PINS

(Output).

When

OE

Is

true, the data

In

the data latches

Is

pre-

sented

as

Inverted

(8283)

or non·lnverted

(8282)

data

onto the data output pins.

8-44

The

8282

and

8283

octal latches are 8·bit latches with

3·state output buffers. Data having satisfied the setup

time requirements is

I.atched

Into the data latches by

strobing the

STe line HIGH

to

LOW.

Holding the

STB

line

In

its active HIGH state makes the latches appear

transparent. Data

Is presented

to

the data output pins by

activating the

~

Input line. When

OE

Is Inactive HIGH·

the output buffers are

In

their high Impedance state.

Enabling or disabling the output buffers will not cause

negatlve·golng transients to appear on the data output

bus.

AFN

oo727B