825318253·5

MODE

2:

Rate Generator. Divide by N counter. The out·

put

will

be

low for one period of the

input

clock. The

period from one

output

pulse

to

the next equals the

number of input counts in the count register.

If the

count

register is reloaded between

output

pulses the

present period

will

not be affected, but the subsequent

period

will reflect the new value.

The gate input, when low, will force the

output

high.

When the gate input goes high, the counter

will start

from the

initial count. Thus, the gate input can be used

to

synchronize the counter.

When this mode is set, the output

will remain high until

after the count register is loaded. The output then can

also be synchronized by software.

MODE

3:

Square Wave Rate Generator.Simi lar to MODE

2 except that the output will remain high until one half

the count has been completed (for even numbers) and

go

low for the other half

of

the count. This is accom·

plished

by

decrementing the counter by two on the fall·

ing edge

oi

each ciock puise. Wilen the counter reaches

terminal count, the state of the output is changed and

the counter is

reloaded with the full count and the whole

process is repeated.

If the count is odd and the output is high, the first

clock

pulse (after the count is loaded) decrements the count

by

1.

Subsequent clock pulses decrement the clock by

2.

After timeout, the output goes low and the full count

is

reloaded. The first clock pulse (following the reload)

decrements the counter

by

3.

Subsequent clock pulses

decrement the count

by

2 until timeout. Then the whole

process is repeated.

In

this way,

if

the count is odd, the

output

will be high for

(N

+ 1)/2 counts and low for

(N

-1)/2

counts.

MODE

4:

Software Triggered Strobe. After the mode is

set, the output

will be high. When the count is loaded,

the counter will begin counting. On terminal count, the

output

will go low

for

one input

clock

period, then will

go high again.

If the count register is reloaded between

output

pulses

the present period

will

not be affected, but the subse-

quent period will reflect the new value. The count will be

inhibited

while the gate input is low. Reloading the

counter register

will

restart counting beginning

with

the

new number.

MODE

5:

Hardware Triggered Strobe. The counter

will

start counting after the rising edge

of

the trigger

input

and will go low

for

one

clock

period when the terminal

count is reached. The counter is retriggerable. The out·

put

will

not go low

until

the full count after the rising

edge

of

any trigger.

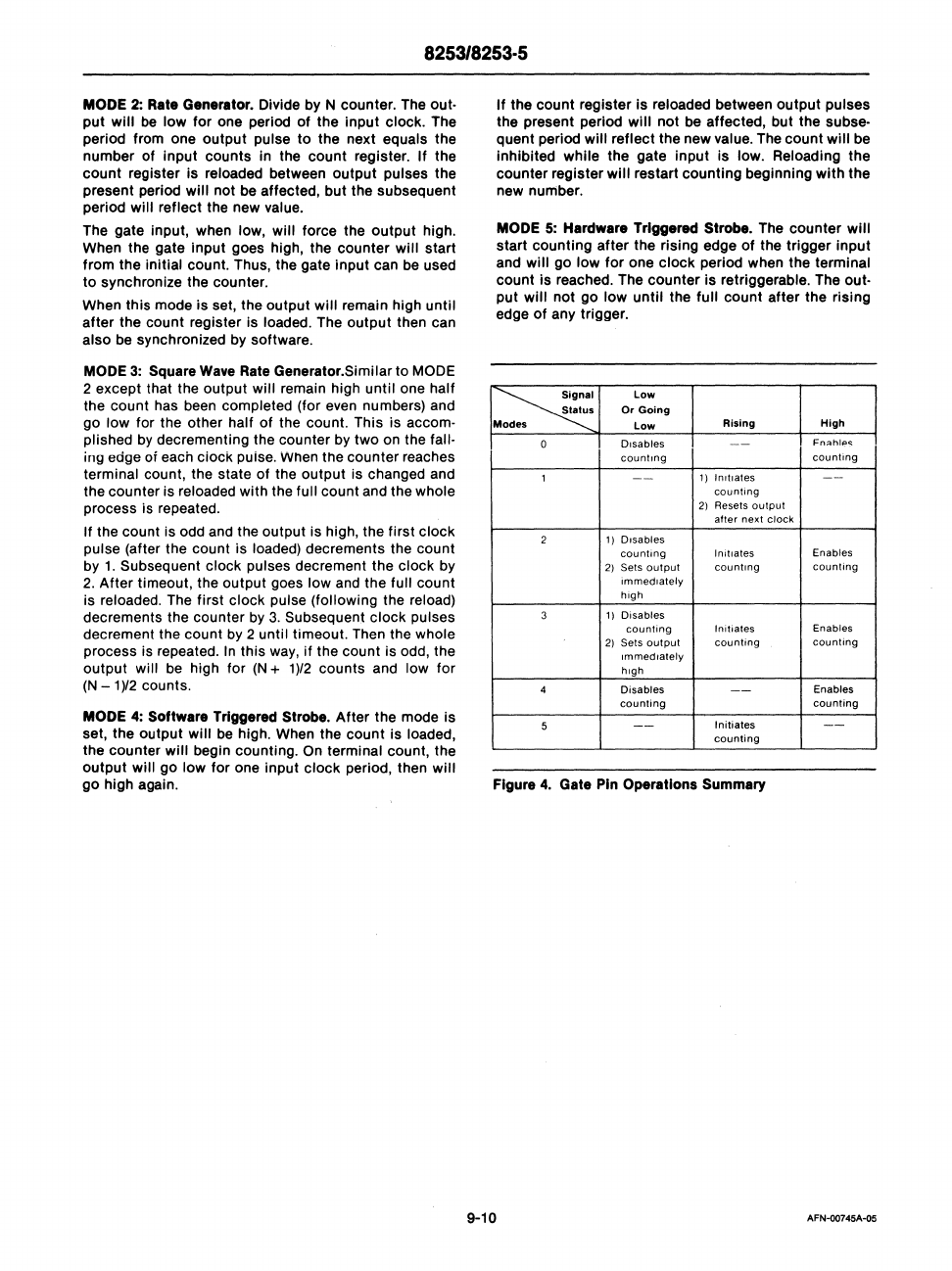

~I

Low

Status

Or

Going

Modes

Low

Rising

High

0

Disables

~~

Fn;:!htp<:;

counting

counting

1

~~

1)

Initiates

~~

counting

2) Resets

output

after

next

clock

2

1)

Disables

counting

Initiates

Enables

2)

Sets

output

counting

counting

immediately

high

3

1)

Disables

counting

Initiates

Enables

2)

Sets

output

counting

counting

Immediately

high

4 Disables

~~

Enables

counting

counting

5

~~

Initiates

~~

counting

Figure

4.

Gate Pin Operations Summary

9-10

AFN-00745A-05