8155/8156/8155-2/8156-2

PROGRAMMING OF THE

COMMAND

REGISTER

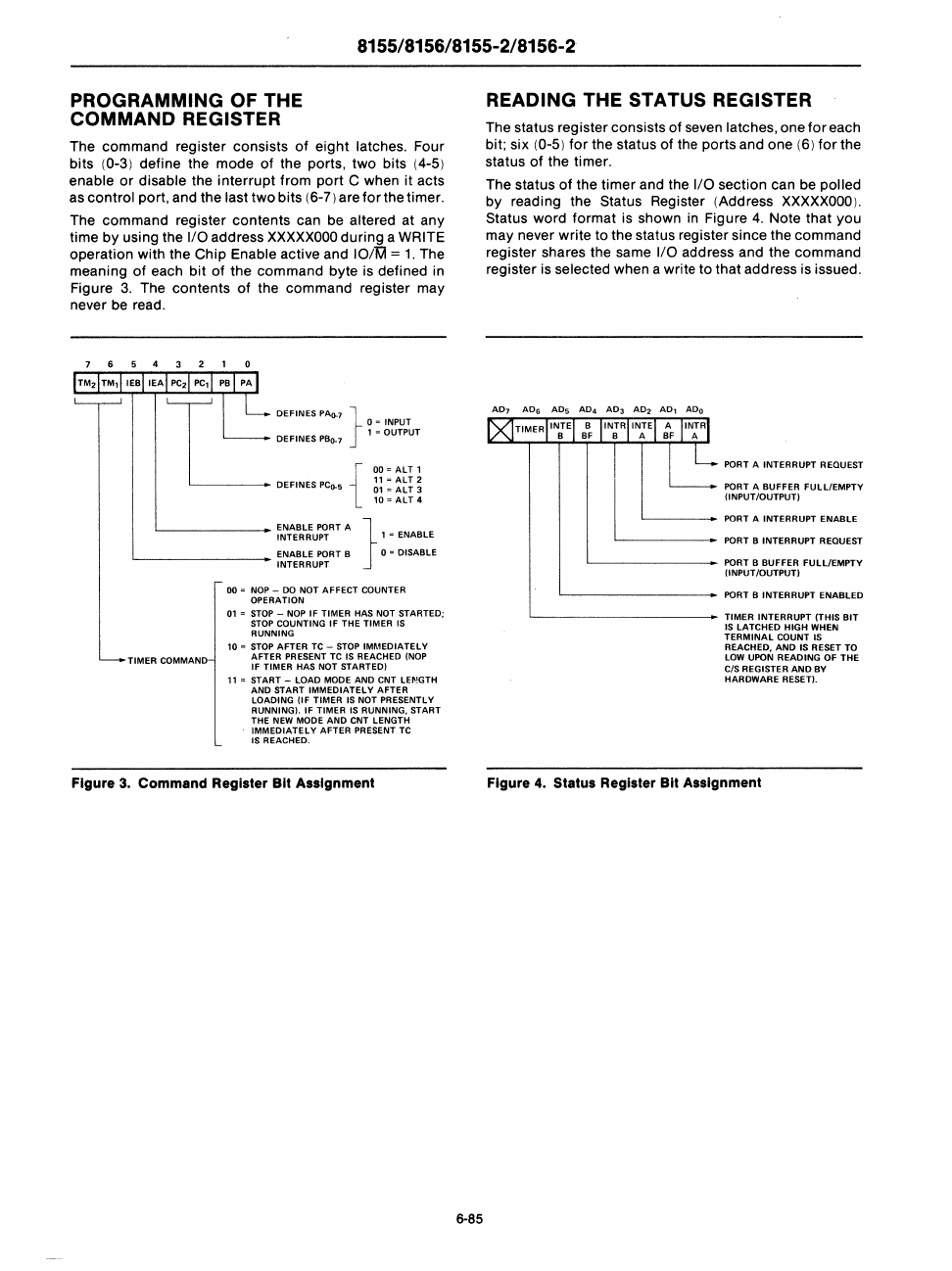

The command register consists of eight latches. Four

bits

(0-3) define the mode of the ports. two bits (4-5)

enable

or

disable the interrupt from

port

C when it acts

as

control port. and the last two bits (6-7)

areforthetimer.

The command register contents can be altered at any

time

by

using the

110

address

XXXXXOOO

during a WRITE

operation with the Chip Enable active and lo/fiil =

1.

The

meaning

of

each bit

of

the command byte is defined in

Figure

3.

The contents

of

the command register may

never be read.

765432

0'"

INPUT

DEFINES

PB()'7

1 = OUTPUT

1:=

DEfINESPA

..

, }

OO"'AlT1

1'=ALT2

DEFINES

PC0-5

{

01

=

At

T 3

10

=

AlT

4

'--------_

~::EBRL:U~RT

A

}

,

..

ENABLE

o·

DISABLE

'---

________

~:::;:U~ATB

"-TIMER

COMMAND

00

= NOP -

00

NOT

AFFECT COUNTER

OPERATION

01

=

STOP

-

NOP

If

TIMER HAS NOT STARTED;

STOP COUNTING

IF

THE TIMER

IS

RUNNING

10 =

STOP

AFTER

Te

-

STOP

IMMEDIATELY

AFTER

PRESENT

Te

IS REACHED (NOP

IF TIMER HAS NOT STARTED)

11

= START - LOAD MODE AND CNT LEfI!GTH

AND START IMMEDIATELY AFTER

LOADING

(IF TIMER

IS

NOT

PRESENTLY

RUNNING).

If

TIMER

IS

RUNNING,

START

THE

NEW

MODE AND CNT LENGTH

IMMEDIATELY AFTER PRESENT

Te

IS REACHED.

Figure

3.

Command Register Bit Assignment

6-85

READING THE STATUS REGISTER

The status register consists of seven latches. one

for

each

bit; six

(0-5)

for

the status of the ports and one

(6)

for

the

status of the timer.

The status

of

the timer and the

I/O

sec.tion can be polled

by reading the Status Register (Address

XXXXXOOO).

Status word format is shown

in

Figure

4.

Note that you

may never write to the status register since the command

register shares the same

I/O address and the command

register is

selected when a write

to

that address is issued.

PORT A INTERRUPT REQUEST

PORT A BUFFER FULL/EMPTY

(INPUT/OUTPUT)

PORT A

INTERRUPT ENABLE

PORT B

INTERRUPT ReQUEST

'---------_

PORT B BUFFER FULL/EMPTY

IINPUTIOUTPUT)

'-----------_

PORT B INTERRUPT ENABLED

'--------------

TIMER INTERRUPT (THIS BIT

IS

LATCHED HIGH

WHEN

TERMINAL COUNT

IS

REACHED,

AND

IS

RESET

TO

LOW

UPON

READING OF THE

CIS REGISTER AND

BY

HARDWARE RESET).

Figure

4.

Status Register Bit Assignment