8253/8253·5

Control Word Register

The

Control

Word

Register is selected when

AD,

A 1 are

11.

It

then accepts

information

from the data bus

buffer

and

stores it in a register. The

information

stored in

this

register

controls

the operational

~~ODE

of

each counter,

selection of

binary

or

BCD

counting

and

the

loading

of

each

count

register.

The

Control

Word Register can

only

be written into; no

read operation

of

its contents is available.

Counter #0, Counter

#1,

Counter

#2

These three

functional

blocks

are identical in operation so

only

a single

Counter

will

be

described. Each

Counter

consists of a single, 16-bit, pre-settable, DOWN counter.

The

counter

can operate in either

binary

or

BCD

and its

input, gate and

output

are

configured

by

the

selection

of

MODES

stored in the

Control

Word Register.

The

counters

are fully

independent

and each can have

separate Mode

configuration

and

counting

operation,

binary

or

BCD. Also, there are special features in

the

control

word

that

handle the loading

of

the

count

value so

that

software overhead can

be

minimized

for

these

functions.

The reading

of

the

contents

of

each

counter

is available

to

the

programmer

with simple READ

operations

for

event

counting

applications and special

commands

and

logic

are

included

in

the

8253 so that

the

contents

of

each

counter

can be read "on the

fly"

without

having

to

inhibit

the

clock

input.

8253 SYSTEM INTERFACE

The 8253 is a

component

of

the

Intel'·

Microcomputer

Systems and interfaces in

the

same

manner

as

all

other

peripherals

of

the

family.

It

is treated

by

the

systems

software

as

an array

of

peripheral

I/O

ports; three are

counters

and

the

fourth

is a

control

register

for

MODE

programming.

Basically, the select

inputs

AD,

A 1

connect

to

the

AD,

A 1

address bus

signals

of

the

CPU. The CS can be derived

directly

from

the

address bus using a linear select method.

Or

it can

be

connected

to

the

output

of

a decoder, such

as

an Intel®

82D5

for

larger systems.

\

l

l

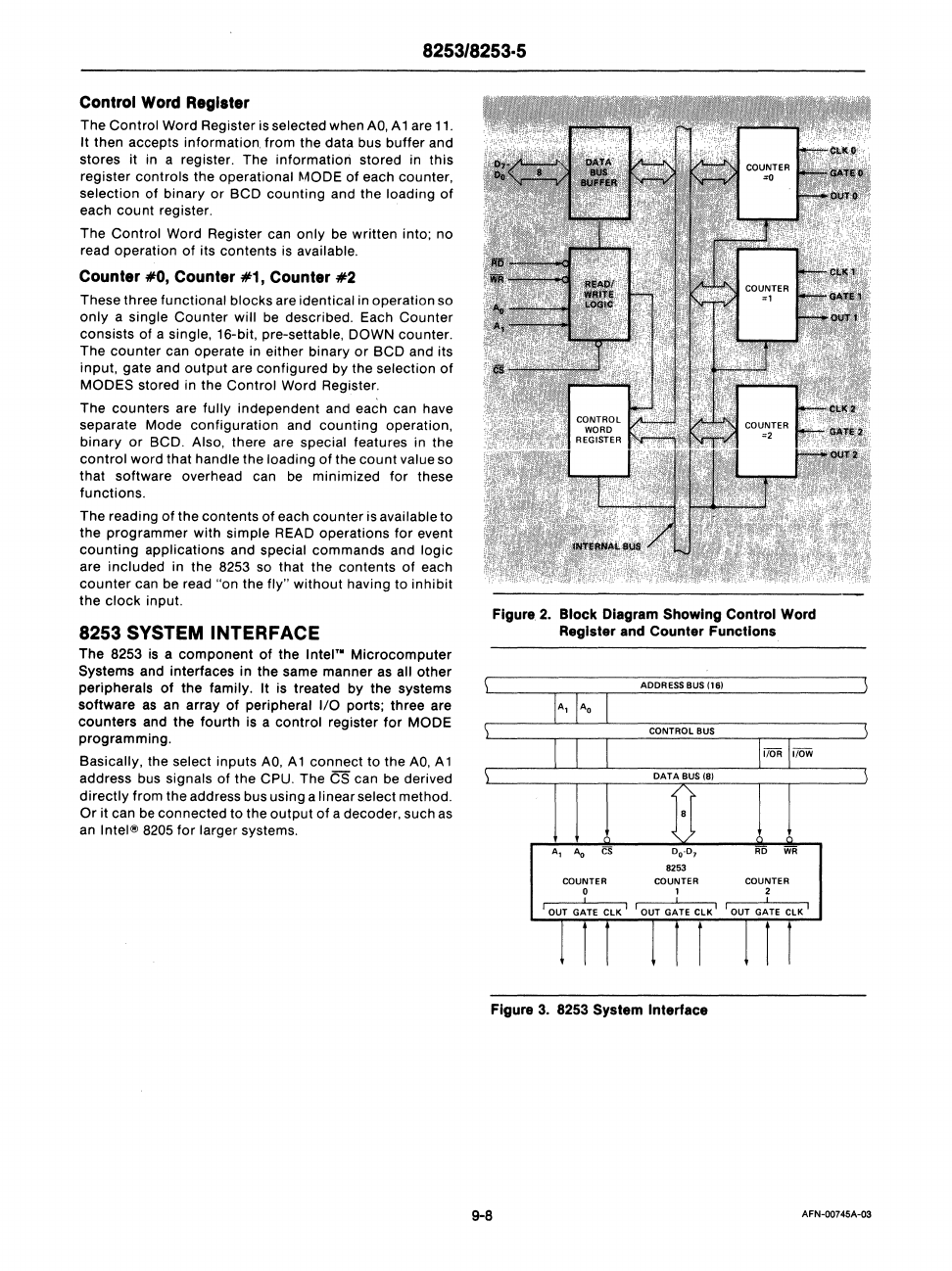

Figure 2. Block Diagram Showing Control Word

Register and Counter Functions

ADDRESS BUS (16)

A,

Ao

CONTROL BUS

liOR

I/OW

DATA

BUS (8)

:·1

A,

Ao

CS

0

0

.0

7

RD

WR

8253

COUNTER

COUNTER

COUNTER

0 1 2

,

lOUT

GATE

elK

I

I

lOUT

GATE

elK'

I

lOUT

GATE

elK

I

j I I

1 I I

j

I

)

\

~

~

Figure

3.

8253 System Interface

9-8

AFN-00745A-03