8255.Al8255A·5

CONTROL WORD

PC2~

1'"

INPUT

o "'OUTPUT

'-----

PORT

B

1'"

INPUT

0=

OUTPUT

'-------

GROUP 8 MODE

0"

MODE

,0

1'"

MODE 1

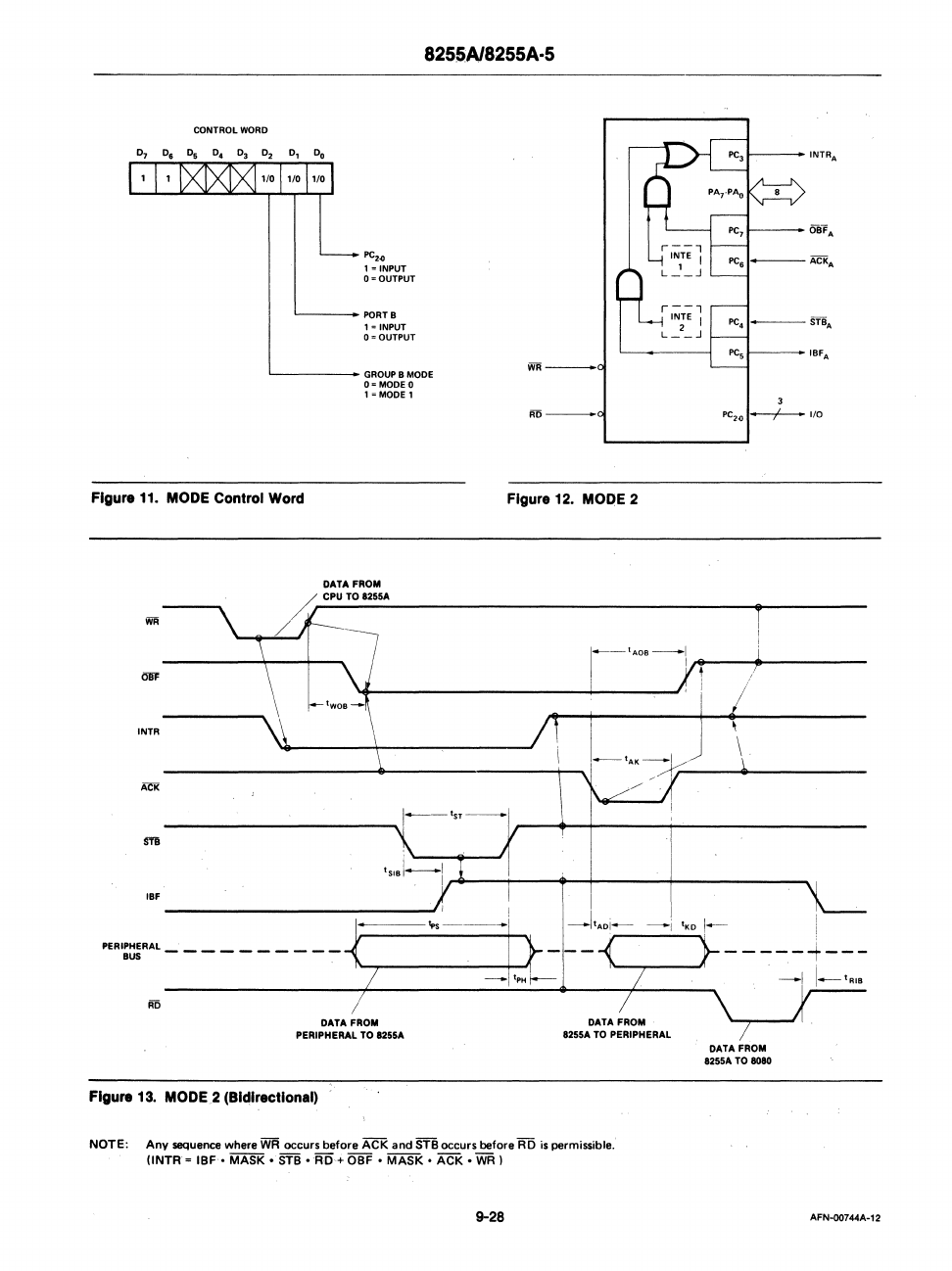

Figure

11.

MODE Control Word

/

INTR

IBF

DATA FROM

/;

CPU TO 8255A

1----""-----

PERIPHERAL

_________

_

BUS

DATA FROM

PERIPHERAL

TO

8255A

Figure

13.

MODE.2 (Bidirectional)

Figure

12.

MODE 2

I

--ltAOi-

r----

.....

NOTE:

Any

sequence where

WR

occurs before

ACK

and STB occurs before RD is permissible.

(lNTR

=

IBF·

MASK·

STB

'RD+

OBF •

MASK·

ACK·

WR)

9-28

------t---

DATA FROM

8255A TO 8080

AFN·OO744A·12