8253/8253·5

OPERATIONAL DESCRIPTION

General

The complete functional definition of the 8253

is

programmed by the systems software. A set

of

control

words must be sent

out

by the CPU to initialize each

counter of the

8253

with the desired MODE and quantity

information. These control words program the

MODE,

Loading sequence and selection of binary or BCD

counting.

Once programmed, the 8253

is

ready

to

perform whatever

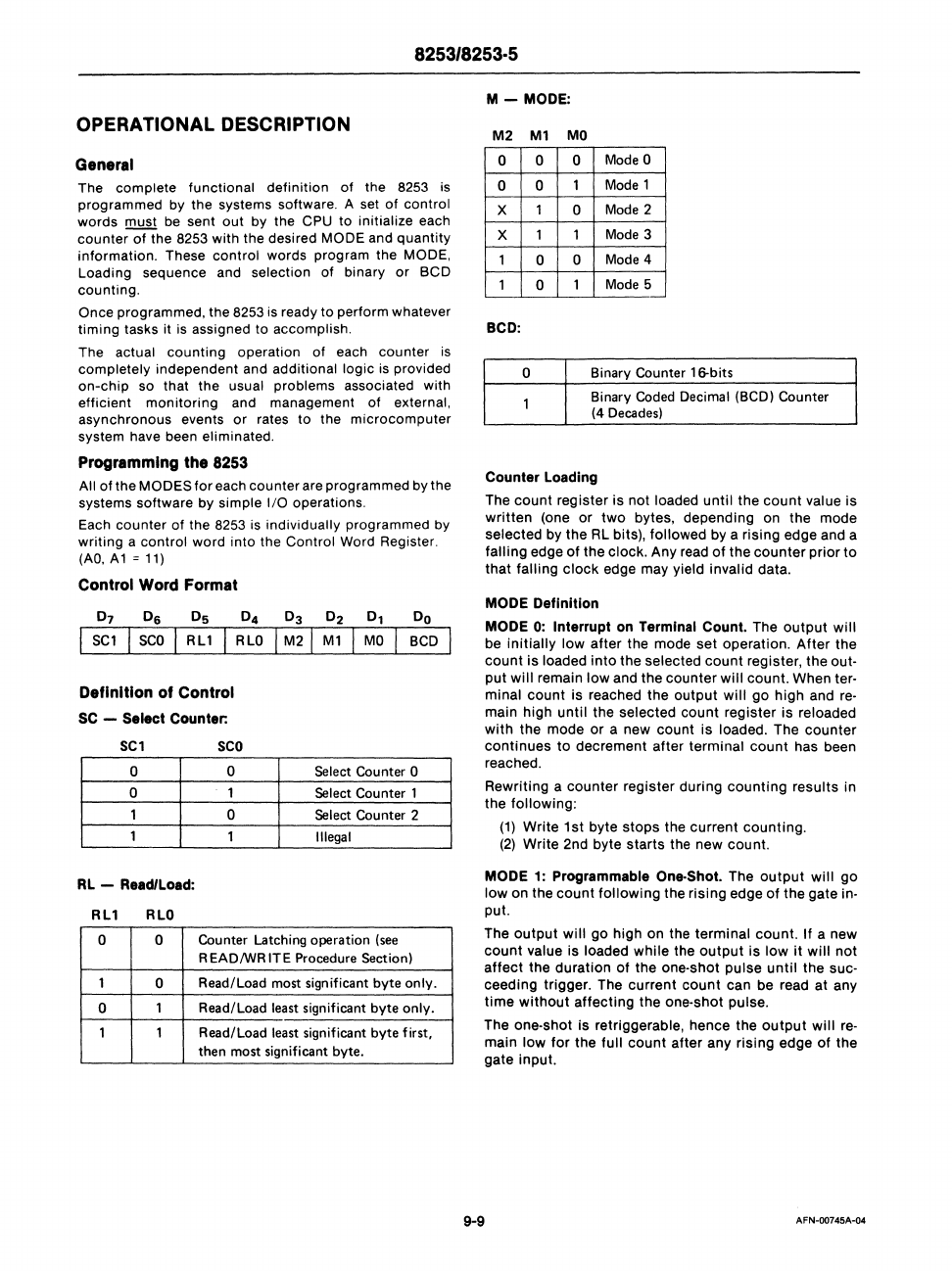

M -

MODE:

M2

Ml

MO

0

0 0

Mode

0

0 0

1

Mode

1

X

1

0

Mode

2

X

1 1

Mode

3

1

0

0

Mode

4

1 0

1

Mode

5

timing tasks it

is

assigned to accomplish. BCD:

The actual counting operation of each counter

is

completely independent and additional logic

is

provided

on-chip

so that the usual problems associated with

efficient monitoring and management of external,

asynchronous events

or

rates to the microcomputer

system have been eliminated.

Programming the

8253

All of the MODES

for

each counter are programmed by the

systems software by simple

I/O

operations.

Each counter of the

8253

is

individually programmed by

writing a control word into the Control Word Register.

(AD,

Al =

11)

Control Word Format

0,

DO

SC1

SCO

RL1

MO

BCD

Definition

of

Control

SC

-

Select

Counter:

SCl

SCO

0

0

Select

Counter 0

0

1

Select

Counter 1

1

0

Select

Counter 2

1

1

Illegal

RL - Read/Load:

RLl

RLO

0 0

Counter Latching operation

(see

R EADIWR ITE Procedure Section)

1

0

Read/Load most significant byte only.

0

1 Read/Load

least

significant byte only.

1

1 Read/Load

least

significant byte first,

then most significant byte.

o

Binary Counter 1

&bits

Binary

Coded

Decimal (BCD) Counter

(4

Decades)

Counter

Loading

The

count

register is not loaded

until

the

count

value is

written

(one or

two

bytes, depending on

the

mode

selected by the RL bits), followed by a rising edge and a

falling edge

of

the clock. Any read

of

the

counter

prior

to

that falling

clock

edge may yield invalid data.

MODE

Definition

MODE

0:

Interrupt on Terminal Count. The

output

will

be

initially

low after the mode

set

operation.

After

the

count

is loaded

into

the selected

count

register, the out·

put will remain low and the counter will count. When ter·

minal

count

is reached

the

output

will

go

high and

re-

main high

until

the selected

count

register

is

reloaded

with

the mode or a new

count

is

loaded. The

counter

continues

to

decrement after terminal

count

has been

reached.

Rewriting a counter register during

counting

results in

the following:

(1)

Write 1st byte

stops

the current

counting.

(2)

Write 2nd byte starts the new count.

MODE

1:

Programmable One·Shot. The

output

will

go

low

on the

count

following

the

rising

edge

of

the gate in-

put.

The

output

will

go

high on the terminal

count.

If a new

count

value is loaded

while

the

output

is 10\\1

it

will

not

affect

the duration

of

the one-shot pulse

until

the suc-

ceeding trigger. The current

count

can be read at any

time

without

affecting

the one-shot pulse.

The one-shot is retriggerable, hence the

output

will

re-

main low

for

the full

count

after any rising edge

of

the

gate input.

9-9

AFN-00745A-Q4