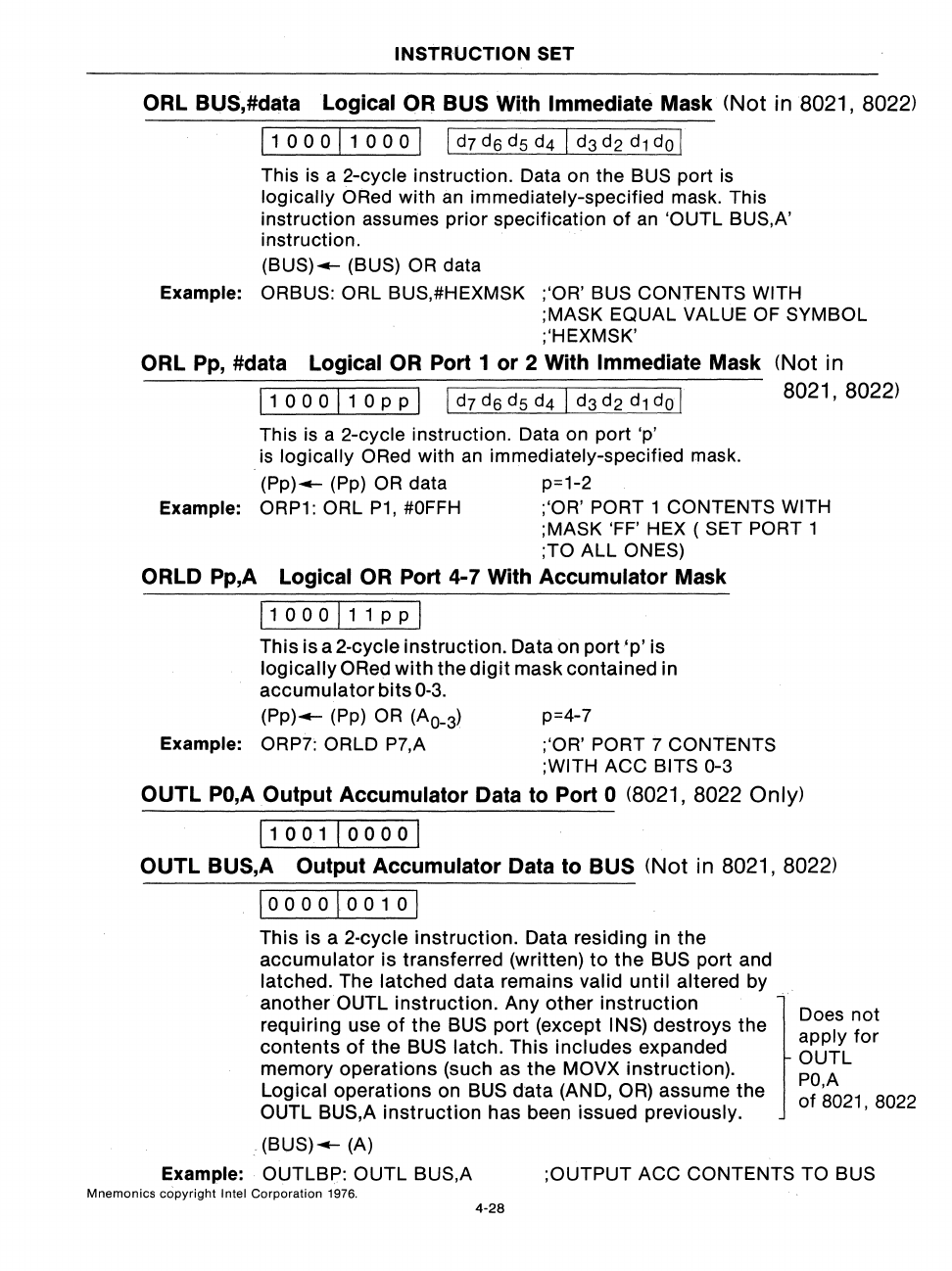

INSTRUCTION SET

ORl

BUS,#data logical

OR

BUS

With

Immediate Mask (Not in 8021,8022)

11

0 0 0

11

0 0 0 1 1

d7

d6

ds

d4

1

d3 d2

d1

do

1

This

is

a 2-cycle instruction. Data on the BUS port

is

logically ORed with

an

immediately-specified mask. This

instruction assumes prior specification

of

an

'OUTL BUS,A'

instruction.

(BUS)--

(BUS)

OR

data

Example: ORB US: ORL BUS,#HEXMSK ;'OR' BUS CONTENTS WITH

;MASK

EQUAL VALUE

OF

SYMBOL

;'HEXMSK'

ORl

Pp,

#data

logical

OR

Port

1

or

2

With

Immediate

Mask

(Not in

11

00

0

11

0 P p 1 1

d7

d6

ds

d4

1

d3

d2

d1

dO

1 8021, 8022)

This

is

a 2-cycle instruction. Data on port 'p'

is

logically ORed with

an

immediately-specified mask.

(Pp)--

(Pp)

OR

data p=1-2

Example: ORP1: ORL

P1,

#OFFH

;'OR' PORT 1 CONTENTS WITH

;MASK

'FF' HEX ( SET PORT 1

;TO ALL ONES)

ORlD

Pp,A

logical

OR

Port

4-7

With

Accumulator

Mask

Example:

11000111ppl

This is a 2-cycle instruction. Data on

port'p'

is

logically

ORed

with

the

digit

mask contained in

accumu

lator

bits

0-3.

(Pp)

...

(Pp)

OR

(AO-3)

ORPT:

ORLD P7,A

p=4-7

;'OR' PORT 7 CONTENTS

;WITH ACC BITS 0-3

OUTl

PO,

A Output Accumulator Data

to

Port 0 (8021, 8022 Only)

11001100001

OUTl

BUS,A Output Accumulator Data

to

BUS (Not in 8021,8022)

100001·00101

This

is

a 2-cycle

instruction.

Data residing in the

accumulator

is transferred (written)

to

the

BUS port and

latched. The latched

data

remains valid

until

altered by

anotherOUTL

instruction.

Any

other

instruction

requiring use

of

the

BUS port (except INS) destroys the

contents

of

the

BUS latch. This includes expanded

memory operations (such as the

MOVX instruction).

Logical operations on BUS

data

(AND,

OR)

assume the

OUTL BUS,A

instruction

has been issued previously .

.

(BUS)

--

(A)

Does not

apply

for

OUTL

PO,A

of

8021, 8022

Example: OUTLB!?: OUTL BUS,A ;OUTPUT ACC CONTENTS TO BUS

Mnemonics copyright Intel Corporation 1976.

4-28