8212

FUNCTIONAL DESCRIPTION

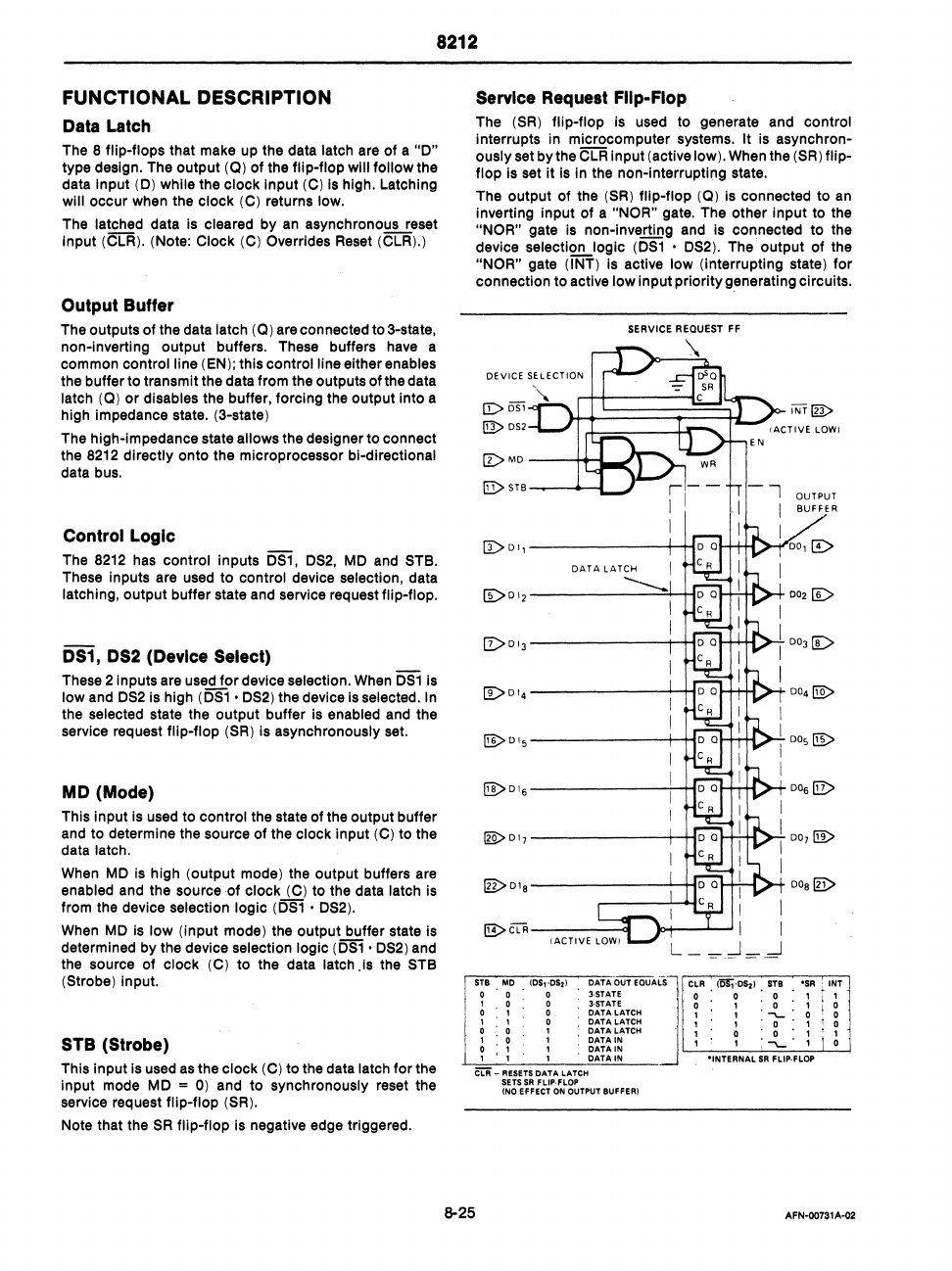

Data Latch

The 8 flip-flops that make up the data latch are of a

"0"

type design. The output

(0)

of the flip-flop will follow the

data Input

(0)

while the clock Input (C)

Is

high. Latching

will occur when the

clock (C) returns low.

The latched data

Is

cleared by

an

asynchronous reset

Input

(CIA).

(Note: Clock (C) Overrides

Reset

(CLR).)

Output Buffer

The outputs of the data latch

(0)

are connected to 3-state,

non-Inverting output buffers. These buffers

have

a

common

control line (EN); this control line either enables

the buffer to transmit the data from the outputs of the data

latch

(0)

or disables the buffer, forcing the output Into a

high Impedance state. (3-state)

The high-impedance state allows the designer to connect

the

8212

directly onto the microprocessor bl-directional

data bus.

Control Logic

The

8212

has

control inputs

OS1,

OS2,

MO

and STB.

These inputs are

used

to control device selection, data

latching, output buffer state and service request flip-flop.

DS1, DS2 (Device Select)

These 2 inputs are

used

for device selection.

When

OS1

Is

low and

OS2

is

high

(OS1

•

OS2)

the device

is

selected.

In

the selected state the output buffer is enabled and the

service request

flip-flop

(SR)

is asynchronously

set.

MD

(Mode)

This input

is

used

to control the state of the output buffer

and to determine the source of the

clock input (C) to the

data

latch.

When

MO

is high (output mode) the output buffers are

enabled and the source of clock (C) to the data latch is

from the device

selection logic

(OS1

•

OS2).

When

MO

is

low (input mode) the output buffer state is

determined by the device

selection logic

(OS1

•

OS2)

and

the source of

clock (C) to the data latch.ls the STB

(Strobe) input.

STB (Strobe)

This input is used

as

the ciock (C) to the data latch for the

input mode

MO

=

0)

and to synchronously reset the

service request

flip-flop (SR).

Note that the

SR

flip-flop

is

negative edge triggered.

Service Request Flip-Flop

The

(SR)

flip-flop is

used

to generate and control

interrupts in microcomputer systems. It is asynchron-

ously set by the

CLR

Input (active low).

When

the

(SR)

flip-

flop is set it

Is

In

the non-Interruptl!lg state.

The output of the

(SR)

flip-flop

(0)

is connected to

an

inverting input of a "NOR" gate. The other Input to the

"NOR" gate

is

non-inverting and

Is

connected to the

device

selection logic

(OS1

•

OS2).

The output of the

"NOR" gate

(00)

Is

active low (interrupting state) for

connection to active

low Input priority generating circuits.

SERVICE

REQUEST

FF

[i>

MD

----+H~rt'

[j)

STa

-..-----i_~

\

Il> D "

--------++1

DATA

LATCH

[Z> D

'3

--------r-+1

IE>

D

'.

--------+-+1

I)]> D 's

--------++1

I)]> D

'6

--------;--+1

[lg> D

'7

--------+-+1

§>D'8-------~+1

STa

.

MO

o

(08,-0

8

21

o

3·STATE

DATA

DUTEClJAJLS

elR

(151;-0121

STa

·SR:

INT

o • • 0 , r 1

,

0

,

,

o

o

·1

o

0,

o

,

,

,

,

3·STATE

DATA

LATCH

DATA

LATCH

DATA

LATCH

.

DATA

IN

DATA

IN

DATA

IN

CLR - RESETS

DATA

LATCH

SETS

SR

FLlp·FLOP

INO

EFFECT

ON

OUTPUT

BUFFERI

8-25

o , 0 • , I 0

~

·;-·~tg

, . 0 • " I '

,

':""'\-.

1 0

-INTERNAL

SR

FLIP·

FLOP

AFN-00731

Ao02