8031/8051/8751

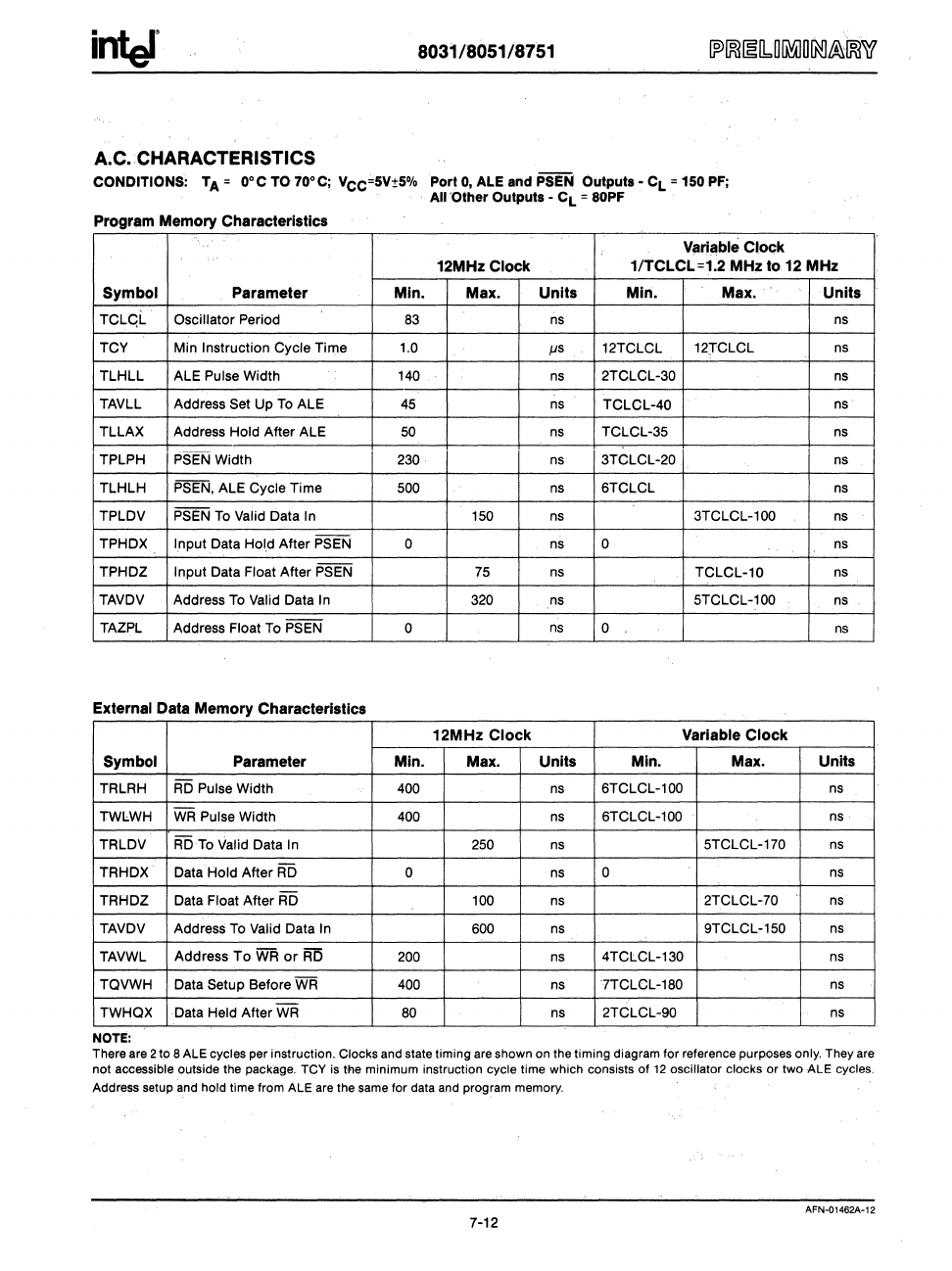

A.C.CHARACTERISTICS

CONDITIONS:

TA

= O°C TO 70°C; VCC=5V±5% Port

0,

ALE

and

PSEN Outputs - CL = 150

PF;

All

Other

Outputs - CL = 80PF

Program Memory Characteristics

....

Variable Clock

12M

Hz Clock

1/TCLCL=1.2 MHz to 12

MHz

Symbol

Parameter

Min. Max.

Units Min. Max. Units

TCLQi..

Oscillator Period

83

ns ns

TCY Min Instruction Cycle Time 1.0

I1

s

12TCLCL

12TCLCL

ns

TLHLL

ALE Pulse Width 140

ns

2TCLCL-30

ns

TAVLL Address Set

Up

To

ALE

45

ns

TCLCL-40

ns

TLLAX

Address Hold After ALE

50

ns

TCLCL-35

ns

TPLPH PSEN Width

230

ns

3TCLCL-20 ns

TLHLH PSEN, ALE Cycle Time

500

ns

6TCLCL ns

TPLDV PSEN

To

Valid Data In 150 ns 3TCLCL-100

ns

TPHDX Input Data Hold After PSEN

0

ns

0

ns

TPHDZ Input Data Float After PSEN

75

ns

TCLCL-10

ns

TAVDV

Address

To

Valid Data In 320 ns

5TCLCL-100

ns

TAZPL Address Float To PSEN

0

ns

0

ns

External Data Memory Characteristics

12MHz

Clock Variable Clock

Symbol

Parameter Min. Max. Units Min.

Max. Units

TRLRH

RD

Pulse Width

400

ns

6TCLCL-100 ns

TWLWH

WR

Pulse Width 400

ns

6TCLCL-100

ns

TRLDV

RDTo

Valid Data In 250 ns

5TCLCL-170

ns

TRHDX Data Hold After RD

0

ns

0

ns

TRHDZ

Data Float After

RD

100

ns

2TCLCL-70

ns

TAVDV

Address

To

Valid Data In 600

ns

9TCLCL-150 ns

TAVWL

Address

To

WR

or

RD

200

ns

4TCLCL-130 ns

TOVWH Data Setup Before

WR

400 ns 7TCLCL-180

ns

TWHOX

Data Held After

WR

80

ns 2TCLCL-90 ns

NOTE:

There are 2 to 8 ALE cycles per instruction. Clocks and state timing are shown on the timing diagram

for

reference purposes only. They are

not

accessible outside the package. TCY is the minimum instruction cycle time which consists of

12

oscillator clocks

or

two

ALE cycles.

Address setup and hold time from ALE are the same for data and program memory.

AFN-01462A-12

7-12