8291

handling procedures. When

an

enabled interrupt bit is

set in either

of

the Interrupt Status Registers, the Input

of

the registers are blocked until the set bit is read and

reset by the microprocessor. Thus, potential problems

arise when interrupt status changes while the register is

being blocked. However, the

8291

stores all new Inter-

rupts in a temporary register and transfers them to the

appropriate interrupt

Status Register after the interrupt

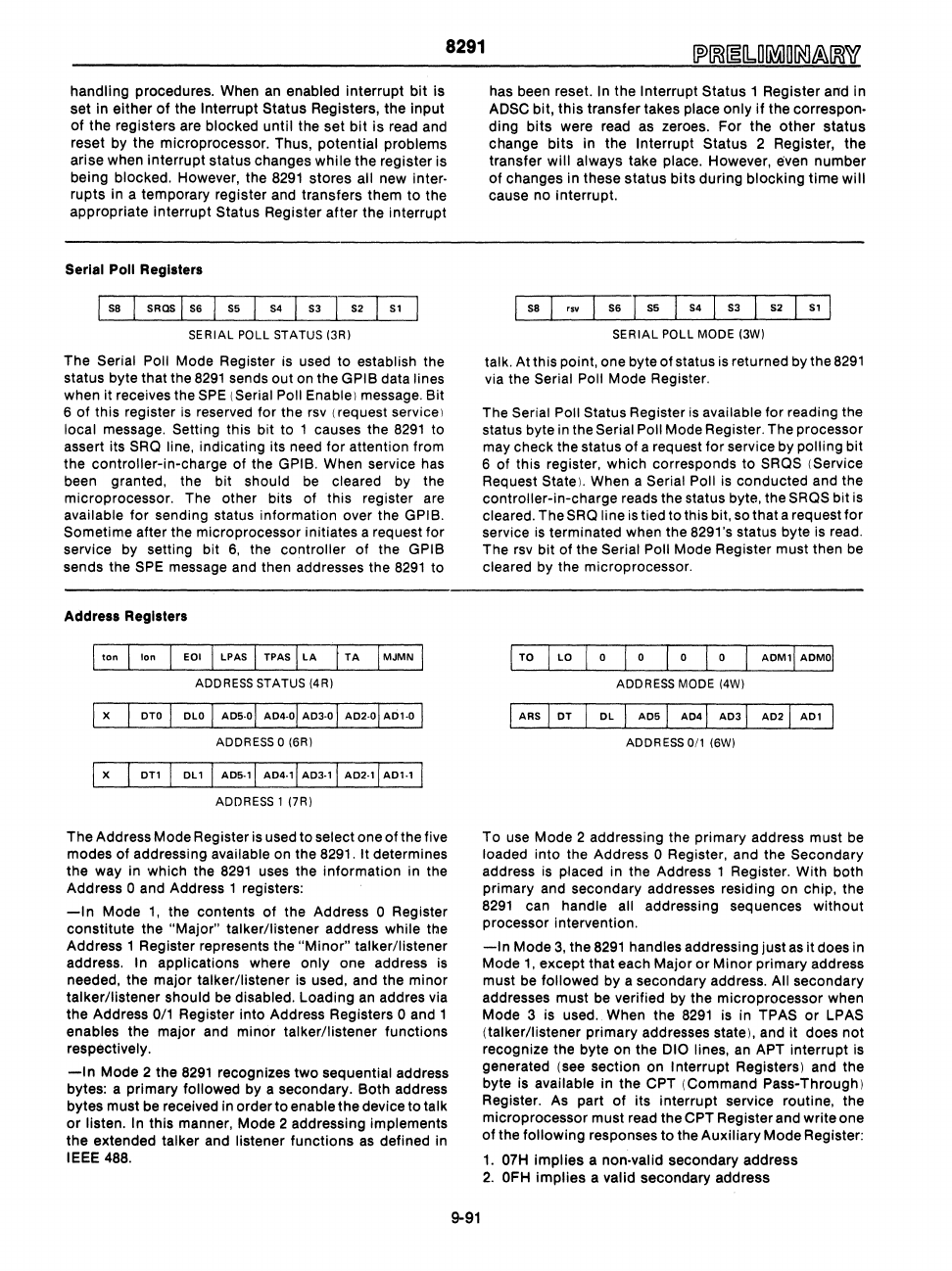

Serial Poll Registers

S8

5Ras

! 56 55

54

53

52

51

SERIAL

POLL STATUS 13R)

The Serial Poll Mode Register

is

used to establish the

status byte that the

8291

sends out on the GPIB data lines

when it receives the

SPE

I Serial Poll Enable I message. Bit

6 of this register

is

reserved for the

rsv

I request service}

local message. Setting this bit to 1 causes the

8291

to

assert its

SRO

line, indicating its need for attention from

the controller-in-charge of the

GPIB. When service has

been granted, the bit should

be

cleared by the

microprocessor. The other bits of this register

are

available for sending status information over the GPIB.

Sometime after the microprocessor initiates a request for

service by setting bit

6,

the controller

of

the GPIB

sends the

SPE

message

and

then addresses the

8291

to

Address Registers

I ton Ion

EOI

!LPAS

!

TPAS

!LA

'[

TA

!MJMN!

ADDRESS STATUS 14R)

I X

OTO!

OLO!

AOS.O!

A04.0!

AD3.0!

AD2.0!

AD,.O

!

ADDRESS 0

16R)

I X

on

DL1!

ADS"!

AD4.1!

AD3.'!

AD2.1!

AD,.,

!

ADDRESS 1 17R)

The Address Mode Register is used to select one of the five

modes of addressing available on the 8291.

It

determines

the way in which the

8291

uses the information in the

Address

0 and Address 1 registers:

-In

Mode

1,

the contents

of

the Address 0 Register

constitute the

"Major" talkerllistener address while tne

Address 1 Register represents the "Minor" talker/listener

address.

In applications where only one address

is

needed, the major talker/listener

is

used, and the minor

talker/listener should

be

disabled. Loading

an

addres via

the Address

0/1

Register into Address Registers 0 and 1

enables the major and

minor talker/listener functions

respectively.

-In

Mode 2 the

8291

recognizes two sequential address

bytes: a primary

followed by a secondary. Both address

bytes must be received in order to enable the device to talk

or

listen. In this manner, Mode 2 addressing implements

the extended talker and listener functions

as

defined in

IEEE

488.

9-91

has been reset.

In

the Interrupt Status 1 Register and in

AOSC

bit, this transfer takes place only

if

the correspon-

ding bits were read as zeroes. For the other status

change bits

In

the Interrupt Status 2 Register, the

transfer will always take place. However,

even number

of changes

In

these status bits during blocking time

will

cause no Interrupt.

58

rsv

56

55

54

53

52

51

SERIAL

POLL MODE

13W)

talk. At this point, one byte of status

is

returned by the

8291

via the Serial Poll Mode Register.

The

Serial Poll Status Register

is

available for reading the

status byte in the

Serial Poll Mode Register. The processor

may check the status of a request for service by

polling bit

6 of this register, which corresponds to

SROS IService

Request State I. When a Serial Poll

is

conducted and the

controller-in-charge reads the status byte, the

SROS

bit

is

cleared. The

SRO

line

is

tied to this bit,

so

that a request for

service

is

terminated when the

8291

's

status byte

is

read.

The rsv bit of the

Serial Poll Mode Register must then

be

cleared by the microprocessor.

I

TO

ILO

I

0

I

0

I

0

I 0

ADM'I

AOMOI

ADDRESS MODE

14WI

!

ARS

!

DT

DL

I

ADS

I

AD41

AD3!

AD2!

AD1

ADDRESS

Oil

16WI

To use Mode 2 addressing the primary address must

be

loaded into the Address 0 Register, and the Secondary

address

is

placed in the Address 1 Register. With both

primary and secondary addresses residing on chip, the

8291

can handle all addressing sequences without

processor intervention.

-In

Mode

3,

the

8291

handles addressing just

as

it

does in

Mode

1,

except that each Major

or

Minor primary address

must

be

followed by a secondary address. All secondary

addresses must

be

verified by the microprocessor when

Mode 3

is

used., When the

8291

is

in TPAS

or

LPAS

(talker/listener primary addresses statel, and it does not

recognize the byte on the

010 lines,

an

APT interrupt

is

generated (see section on Interrupt Registers) and the

byte is available in the CPT (Command Pass-Through)

Register.

As

part

of

its interrupt service routine, the

microprocessor must read the CPT Register and write one

of

the following responses to the Auxiliary Mode Register:

1.

07H

implies a non-valid secondary address

2.

OFH

implies a valid secondary address