8291

GPIB TALKER/LISTENER

• Designed

to

Interface Microprocessors

(e.g.,

8080, 8085, 8086, 8048)

to

an

IEEE Standard 488 Digital Interface

Bus

• Programmable Data Transfer Rate

• Complete Source and

Acceptor

Handshake

• Complete Talker and Listener

Functions with Extended Addressing

• Service Request; Paralle! Poll, Device

Clear, Device Trigger, Remote/Local

Functions

• Selectable Interrupts

•

On-Chip

Primary and Secondary

Address Recognition

•

Automatic

Handling

of

Addressing and

Handshake Protocol

• Provision

for

Software Implementation

of

Additional Features

•

1-8

MHz

Clock

Range

• 16 Registers (8 Read, 8 Write), 2

for

Data Transfer, the Rest

for

Interface

Function Control, Status, etc.

•

Directly

Interfaces

to

External

Non-

Inverting Transceivers

for

Connection

to

the GPIB

•

Provides Three Addressing Modes,

Allowing

the

Chip

to

be Addressed

Either as a

Major

or

a

Minor

Talkerl

Listener with Primary

or

Secondary

Addressing

•

DMA

Handshake Provision Allows

for

Bus Transfers

without

CPU Intervention

•

Trigger

Output

Pin

•

On-Chip

EOS (End

of

Sequence)

Message Recognition Facilitates

Handling

of

Multi-Byte

Transfers

The

8291

GPIB

Talker/Listener is a microprocessor-controlled chip designed

to

interface microprocessors (e.g.,

8048;

8080,8085,8086) to

an

IEEE

Standard

488

Instrumentation Interface Bus. It implements all

of

the Standard's interface

functions except for

the.

controller.

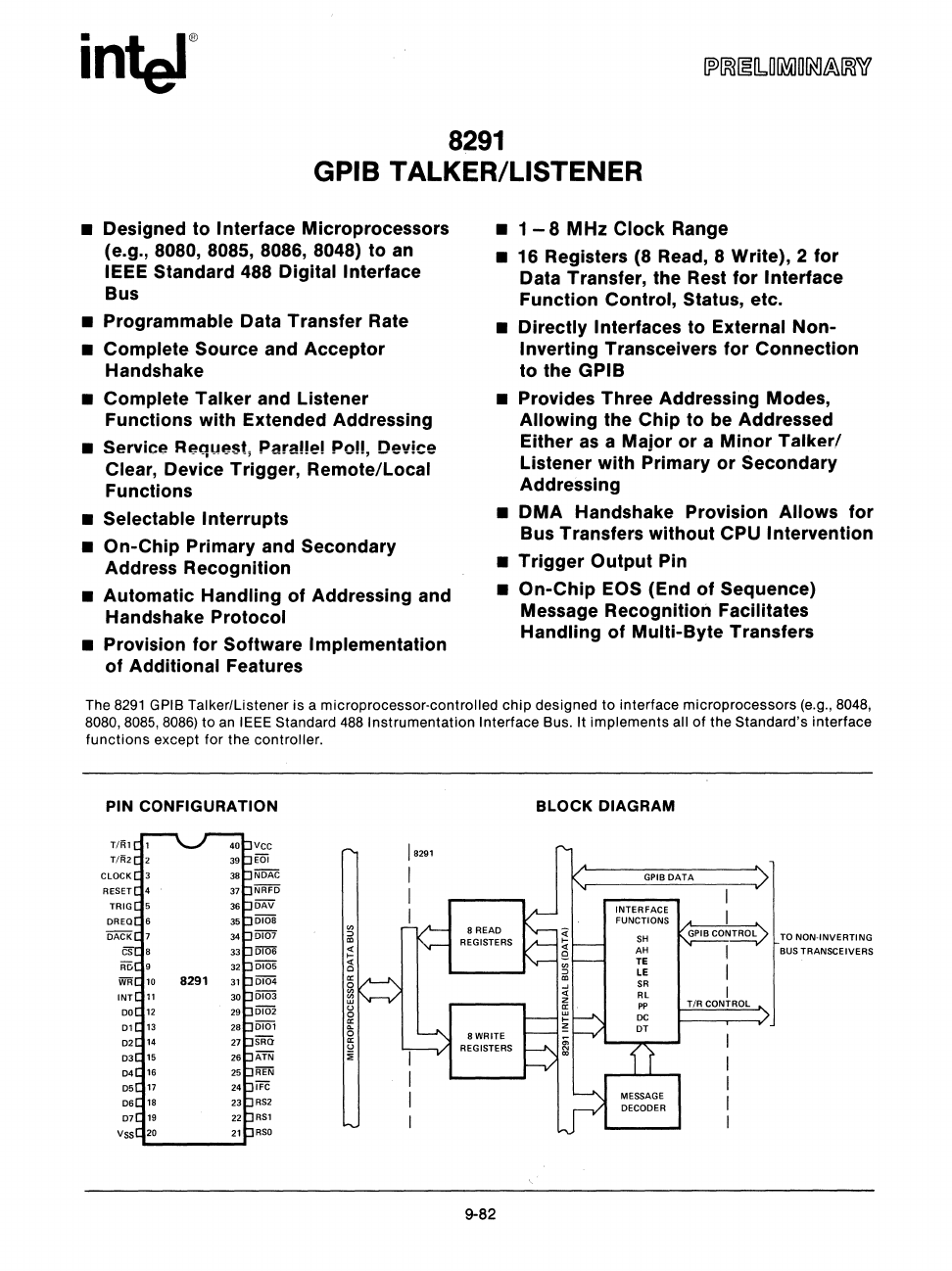

PIN

CONFIGURATION

9-82

BLOCK

DIAGRAM

GPIB DATA

INTERFACE

FUNCTIONS

~===-=".

SH

GPIB CONTROL

AH

TE

LE

I

T/RCONTROL

TO NON-INVERTING

BUS TRANSCEIVERS