2732A

32K

(4K x

8)

UV

ERASABLE

PROM

•

200ns

(2732A·2)

Maximum

Access

Time

...

HMOS*·E

Technology

•

Compatible

to

High

Speed

8mHz

8086·2

MPU

..

.

Zero

WAIT

State

•

Two

Line

Control

•

Pin

Compatible

to

2764

EPROM

• Industry

Standard

Pinout

.

..

JEDEC

Approved

•

Low

Standby

Current

.

..

35mA

Max.

The Intel

2732A

Is a 5Vonly,

32,384

bit ultraviolet erasable and electrically programmable read-only memory

(EPROM).

It

Is

pin

compatl~le

to Intel's 450ns

2732.

The standard 2732A's access time is 250ns with speed selection

(2732A-2)

available at 200ns. The access time is compatible

to

high performance microprocessors, such as the 8mHz

8086-2.

In

these systems, the 2732A allows the microprocessor

to

operate without the addition

of

WAIT states.

An

Important

2732A

feature is the separate output control, Output Enable

(OE),

from the Chip Enable control

(CE).

The

OE

control eliminates bus contention

in

multiple bus microprocessor systems. Intel's Application Note

AP-72

describes the

microprocessor system

implementation

of

the

OE

and CEcontrols

on

Intel's

EPROMs.

AP-72

Is available from Intel's

Literature Department.

The

2732A

has a standby mode which reduces the power dissipation without increasing access time. The maximum

active current

Is 150mA, while the maximum standby current is only 35mA, a 75% saving.

The

standby mode Is achieved

by

applying a TTL-high signal

to

the

CE

input.

The 2732A

Is fabricated with HMOS*-E technology, Intel's high speed N-channel

MOS

Silicon Gate Technology.

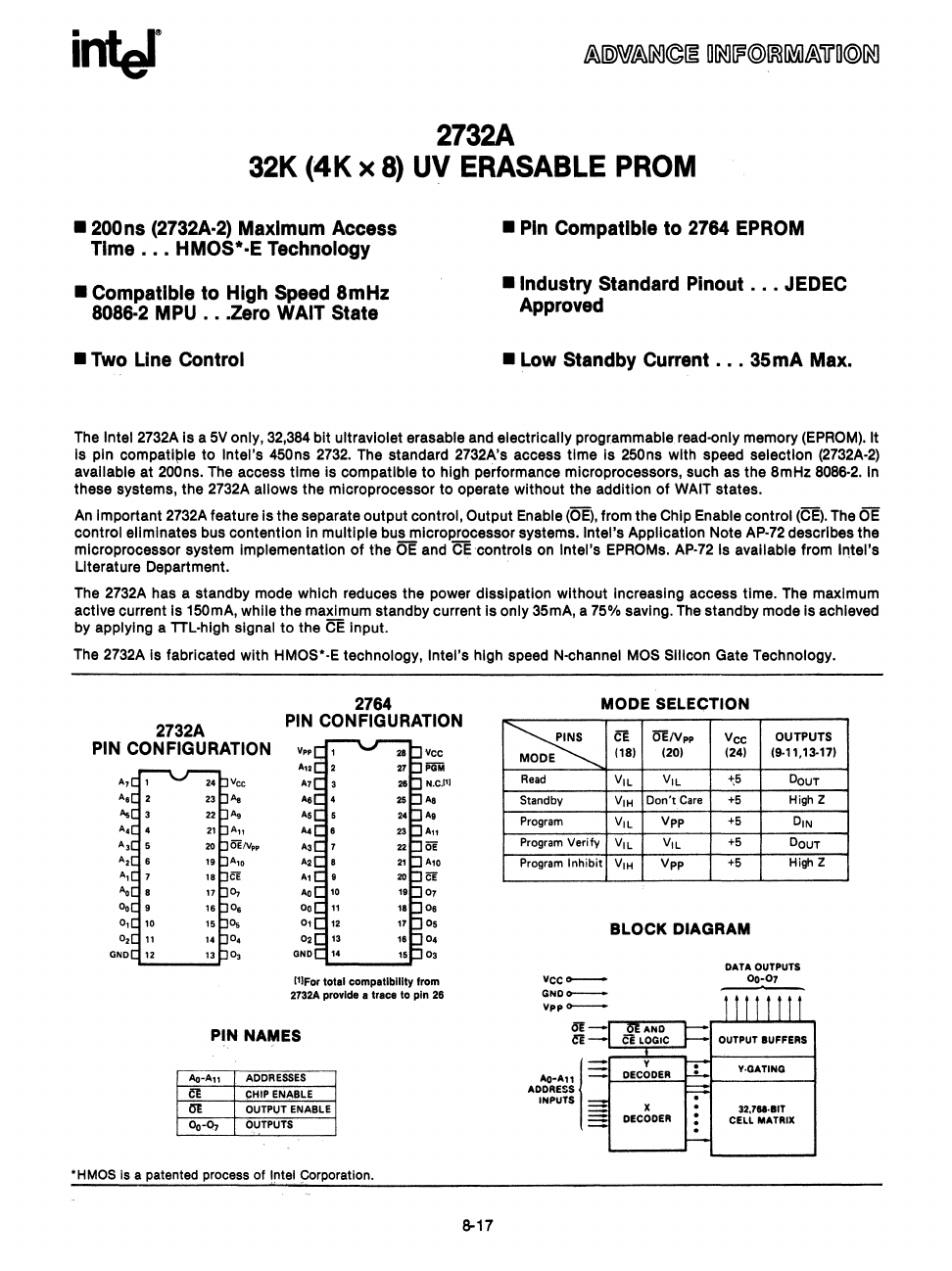

2764

2732A

PIN CONFIGURATION

PIN CONFIGURATION

v,,

'Vee

An

POM

A1

N.CJ11

As

A8

A,

Ag

A,

A11

A3

OE

A.

A,O

A,

CE

AO

00

0,

0,

o.

0,

GND

03

('(For total compatibility from

2732A

provide a trace to pin

26

PIN NAMES

AO-Al1

ADDRESSES

CE

CHIP

ENABLE

~

OUTPUT

ENABLE

°o-Or

OUTPUTS

·HMOS

Is

a patented process of Intel Corporation.

8-17

MODE SELECTION

~

MODE

Read

Standby

Program

Program Veri

Iy

Program

Inhibit

VCC~

GNDO----

AQ-A"

ADDRESS

INPUTS

-

CE

OENpp

Vcc

OUTPUTS

(18) (20) (24)

(9·11,13·17)

VIL

VIL

-+;5

DOUT

VIH

Don't

Care

+5

High Z

VIL

Vpp

+5

DIN

VIL

VIL

+5

DOUT

VIH

Vpp

+5

High Z

BLOCK DIAGRAM

X

DECODER

DATA OUTPUTS

00-07

Y·GATING

32.788·8IT

CELL

MATRIX