5-9

MEMORY PARTITIONS

NOTE

Using any SFR as a base or index register for indirect or indexed operations

can cause unpredictable results because external events can change the

contents of SFRs. Also, because some SFRs are cleared when read, consider

the implications of using an SFR as an operand in a read-modify-write

instruction (e.g., XORB).

5.2.4 Register File

The register file is divided into an upper register file and a lower register file (Figure 5-3). The

upper register file consists of general-purpose register RAM. The lower register file contains ad-

ditional general-purpose register RAM along with the stack pointer (SP) and the CPU special-

function registers (SFRs).

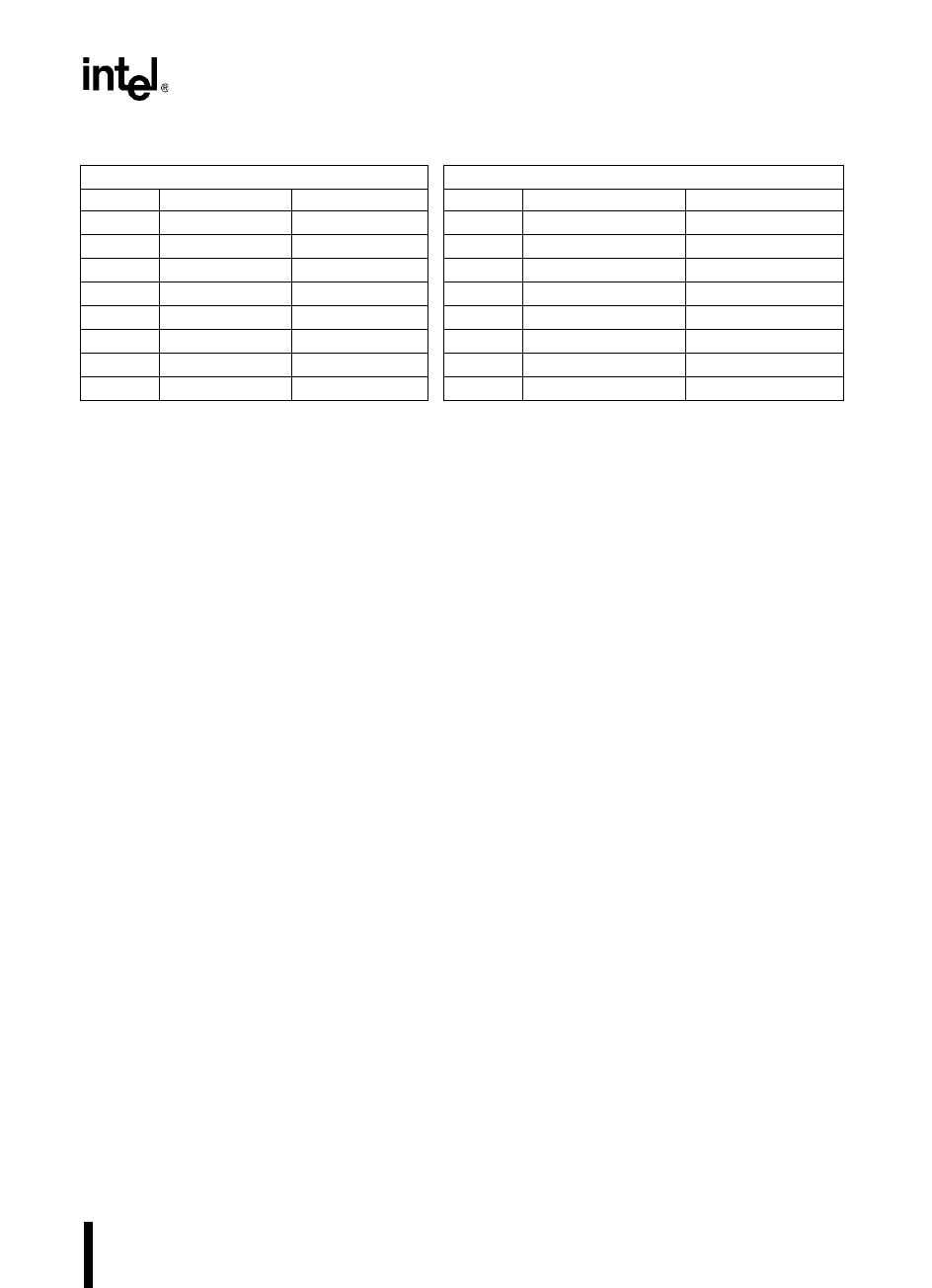

EPA, Timer 1, and Timer 2 SFRs (Continued) Chip-select SFRs (Continued)

Address High (Odd) Byte Low (Even) Byte Address High (Odd) Byte Low (Even) Byte

1F7EH Reserved Reserved 1F4EH Reserved Reserved

1F7CH Reserved Reserved 1F4CH Reserved BUSCON1

1F7AH Reserved Reserved 1F4AH ADDRMSK1 (H) ADDRMSK1 (L)

1F78H Reserved Reserved 1F48H ADDRCOM1 (H) ADDRCOM1 (L)

1F76H Reserved Reserved 1F46H Signature (H)

††††

Signature (L)

††††

1F74H Reserved Reserved 1F44H Reserved BUSCON0

1F72H Reserved Reserved 1F42H ADDRMSK0 (H) ADDRMSK0 (L)

1F70H Reserved Reserved 1F40H ADDRCOM0 (H) ADDRCOM0 (L)

Table 5-5. Peripheral SFRs (Continued)

†

Must be addressed as a word.

††

For the 8XC196NP, these are memory-mapped locations. They must be addressed with indirect or

indexed instructions, and they cannot be windowed.

†††

The EPA_PEND register was called EPA_STAT in previous documentation for the 8XC196NP.

††††

The 8XC196NP can be identified by its signature word, 80EFH, at locations 1F46–1F47H. The

8XC196NU has no signature word; locations 1F46–1F47H are reserved.