13-1

CHAPTER 13

INTERFACING WITH EXTERNAL MEMORY

The device can interface with a variety of external memory devices. Six chip-selects can be indi-

vidually programmed for bus width, the number of wait states, and a multiplexed or demulti-

plexed address/data bus. Other features of the external memory interface include ready control

for inserting additional wait states, a bus-hold protocol that enables external devices to take con-

trol of the bus, and two write-control modes for writing words and bytes to memory. These fea-

tures provide a great deal of flexibility when interfacing with external memory devices.

In addition to describing the signals and registers related to external memory, this chapter discuss-

es the process of fetching the chip configuration bytes and configuring the external bus. It also

provides examples of external memory configurations and chip-select setup.

13.1 INTERNAL AND EXTERNAL ADDRESSES

The address that external devices see is different from the address that the device generates inter-

nally. Internally, the device has 24 address lines, but only the lower 20 address lines (A19:0)

are implemented with external pins. The absence of the upper four address bits at the external pins

causes different internal addresses to have the same external address. For example, the internal

addresses FF2080H, 7F2080H, and 0F2080H all appear at the 20 external pins as F2080H. The

upper nibble of the internal address has no effect on the external address.

The address seen by an external device also depends on the number of address lines that the ex-

ternal system uses. If the address on the external pins (A19:0) is F2080H, and only A17:0 are con-

nected to the external device, the external device sees 32080H. The upper four address lines

(A19:16) are implemented by the EPORT. Table 13-1 shows how the external address depends

on the number of EPORT lines used to address the external device.

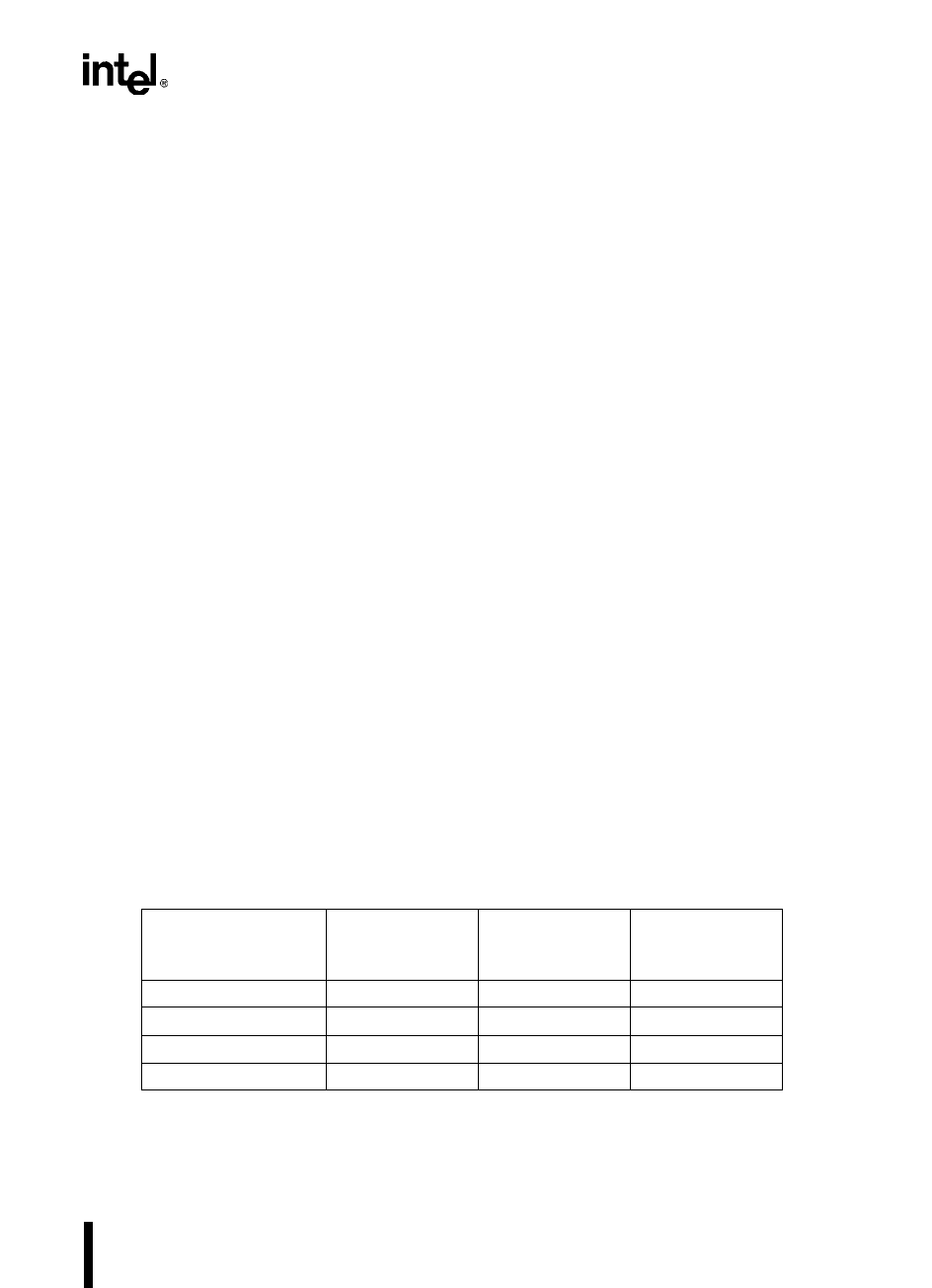

Table 13-1. Example of Internal and External Addresses

EPORT Lines

Connected to the

External Device

Internal Address

Address on the

Device Pins

Address Seen by

External Device

A16

x

F2080H F2080H 12080H

A17:16

x

F2080H F2080H 32080H

A18:16

x

F2080H F2080H 72080H

A19:16

x

F2080H F2080H F2080H