A-59

INSTRUCTION SET REFERENCE

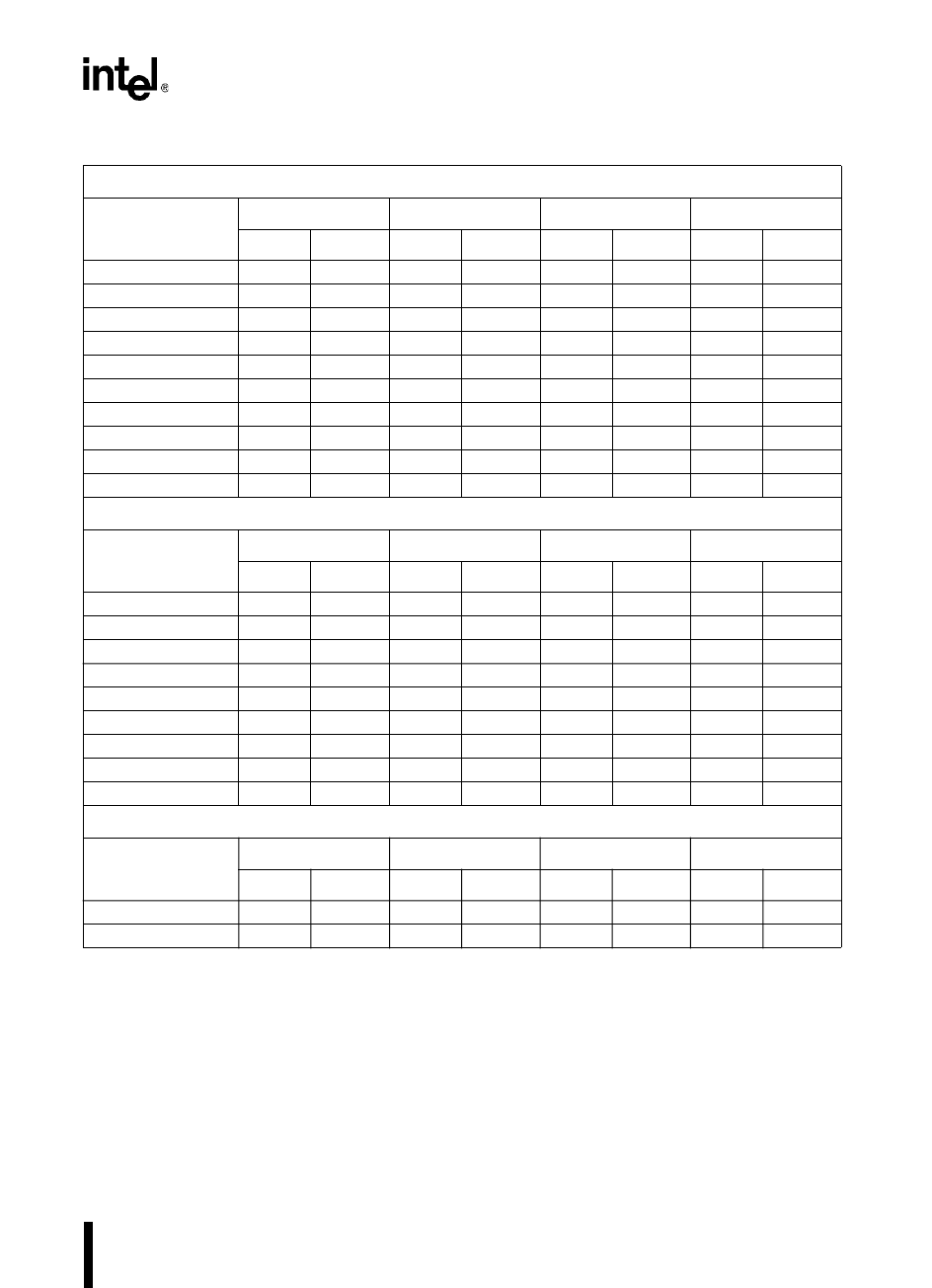

Shift

Mnemonic

Direct Immediate Indirect Indexed

Length Opcode Length Opcode Length Opcode Length Opcode

NORML 3 0F ——————

SHL 309——————

SHLB 319——————

SHLL 30D——————

SHR 308——————

SHRA 30A——————

SHRAB 31A——————

SHRAL 30E——————

SHRB 318——————

SHRL 30C——————

Special

Mnemonic

Direct Immediate Indirect Indexed

Length Opcode Length Opcode Length Opcode Length Opcode

CLRC 1F8——————

CLRVT 1FC——————

DI 1FA——————

EI 1FB——————

IDLPD — — 1 F6 — — — —

NOP 1FD——————

RST 1FF——————

SETC 1F9——————

SKIP 200——————

PTS

Mnemonic

Direct Immediate Indirect Indexed

Length Opcode Length Opcode Length Opcode Length Opcode

DPTS 1 EC ——————

EPTS 1ED——————

Table A-8. Instruction Lengths and Hexadecimal Opcodes (Continued)

NOTES:

1. Indirect normal and indirect autoincrement share the same opcodes, as do short- and long-indexed

modes. Because word registers always have even addresses, the address can be expressed in the

upper seven bits; the least-significant bit determines the addressing mode. Indirect normal and short-

indexed modes make the second byte of the instruction even (LSB = 0). Indirect autoincrement and

long-indexed modes make the second byte odd (LSB = 1).

2. For indexed instructions, the first column lists instruction lengths as

S

/

L

, where

S

is the short-indexed

instruction length and

L

is the long-indexed instruction length.

3. For the SCALL and SJMP instructions, the three least-significant bits of the opcode are concatenated

with the eight bits to form an 11-bit, 2’s complement offset.