8XC196NP, 80C196NU USER’S MANUAL

B-8

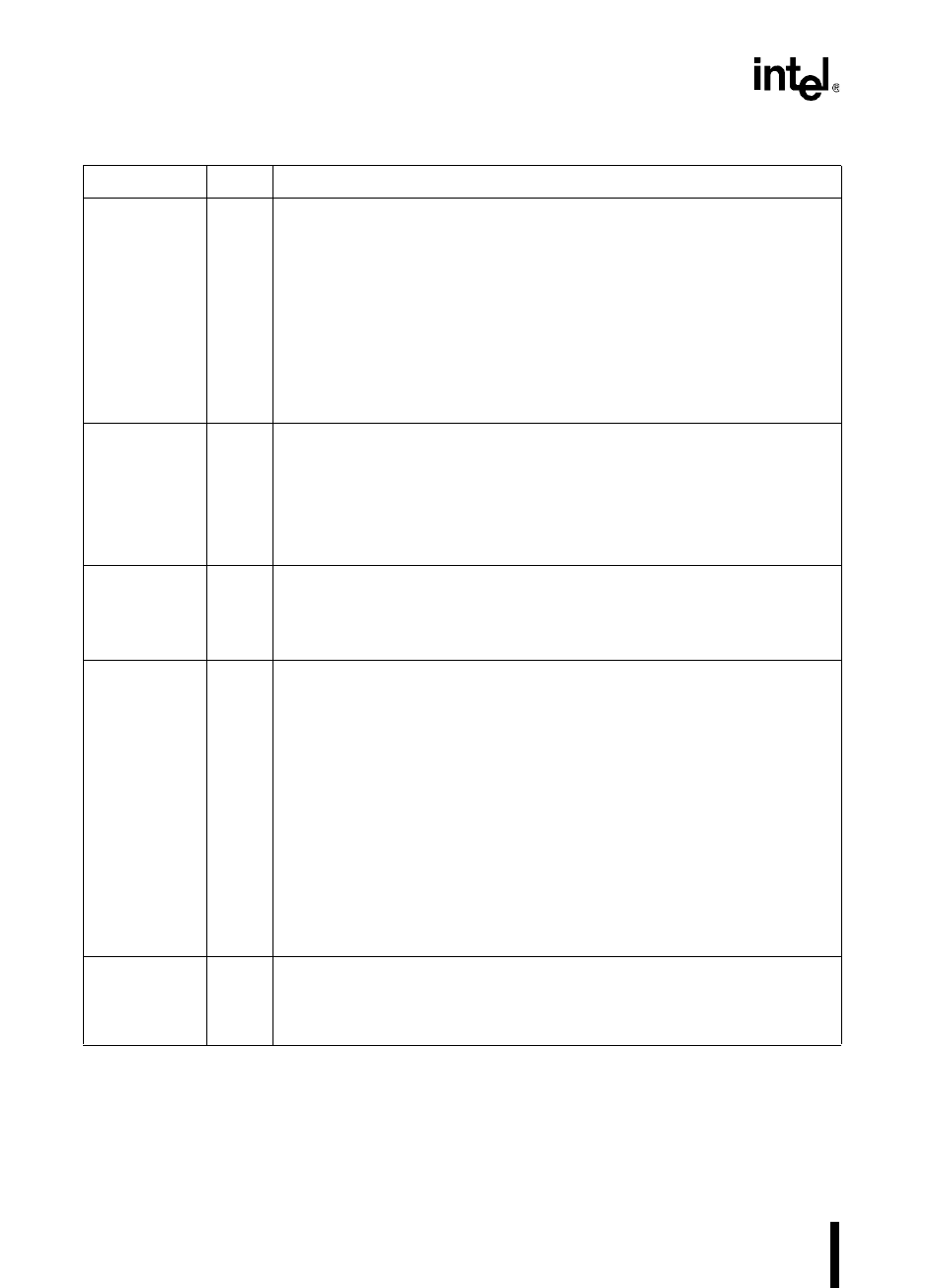

EA# (NP only) I External Access

This input determines whether memory accesses to special-purpose and

program memory partitions (FF2000–FF2FFFH) are directed to internal or

external memory. These accesses are directed to internal memory if EA# is

held high and to external memory if EA# is held low. For an access to any other

memory location, the value of EA# is irrelevant.

EA# is not latched and can be switched dynamically during normal operating

mode. Be sure to thoroughly consider the issues, such as different access times

for internal and external memory, before using this dynamic switching capability.

On devices with no internal nonvolatile memory, always connect EA# to V

SS

.

EA# is not implemented on the 80C196NU.

EPA3:0 I/O Event Processor Array (EPA) Input/Output pins

These are the high-speed input/output pins for the EPA capture/compare

channels. For high-speed PWM applications, the outputs of two EPA channels

(either EPA0 and EPA1 or EPA2 and EPA3) can be remapped to produce a

PWM waveform on a shared output pin (see “Generating a High-speed PWM

Output” on page 10-14).

EPA3:0 are multiplexed with P1.3:0.

EPORT.3:0 I/O Extended Addressing Port

On the 8XC196NP, this is a 4-bit, bidirectional, memory-mapped I/O port.

On the 8XC196NU, this is a 4-bit, bidirectional, standard I/O port.

EPORT.3:0 are multiplexed with A19:16.

EXTINT3:0 I External Interrupts

In normal operating mode, a rising edge on EXTINT

x

sets the EXTINT

x

interrupt pending bit. EXTINT

x

is sampled during phase 2 (CLKOUT high). The

minimum high time is one state time.

In standby and powerdown modes, asserting the EXTINT

x

signal for at least 50

ns causes the device to resume normal operation. The interrupt need not be

enabled, but the pin must be configured as a special-function input (see

“Bidirectional Port Pin Configurations” on page 7-7). If the EXTINT

x

interrupt is

enabled, the CPU executes the interrupt service routine. Otherwise, the CPU

executes the instruction that immediately follows the command that invoked the

power-saving mode.

In idle mode, asserting any enabled interrupt causes the device to resume

normal operation.

EXTINT0 is multiplexed with P2.2, EXTINT1 is multiplexed with P2.4, EXTINT2

is multiplexed with P3.6, and EXTINT3 is multiplexed with P3.7.

HLDA# O Bus Hold Acknowledge

This active-low output indicates that the CPU has released the bus as the result

of an external device asserting HOLD#.

HLDA# is multiplexed with P2.6.

Table B-3. Signal Descriptions (Continued)

Name Type Description