8XC196NP, 80C196NU USER’S MANUAL

13-4

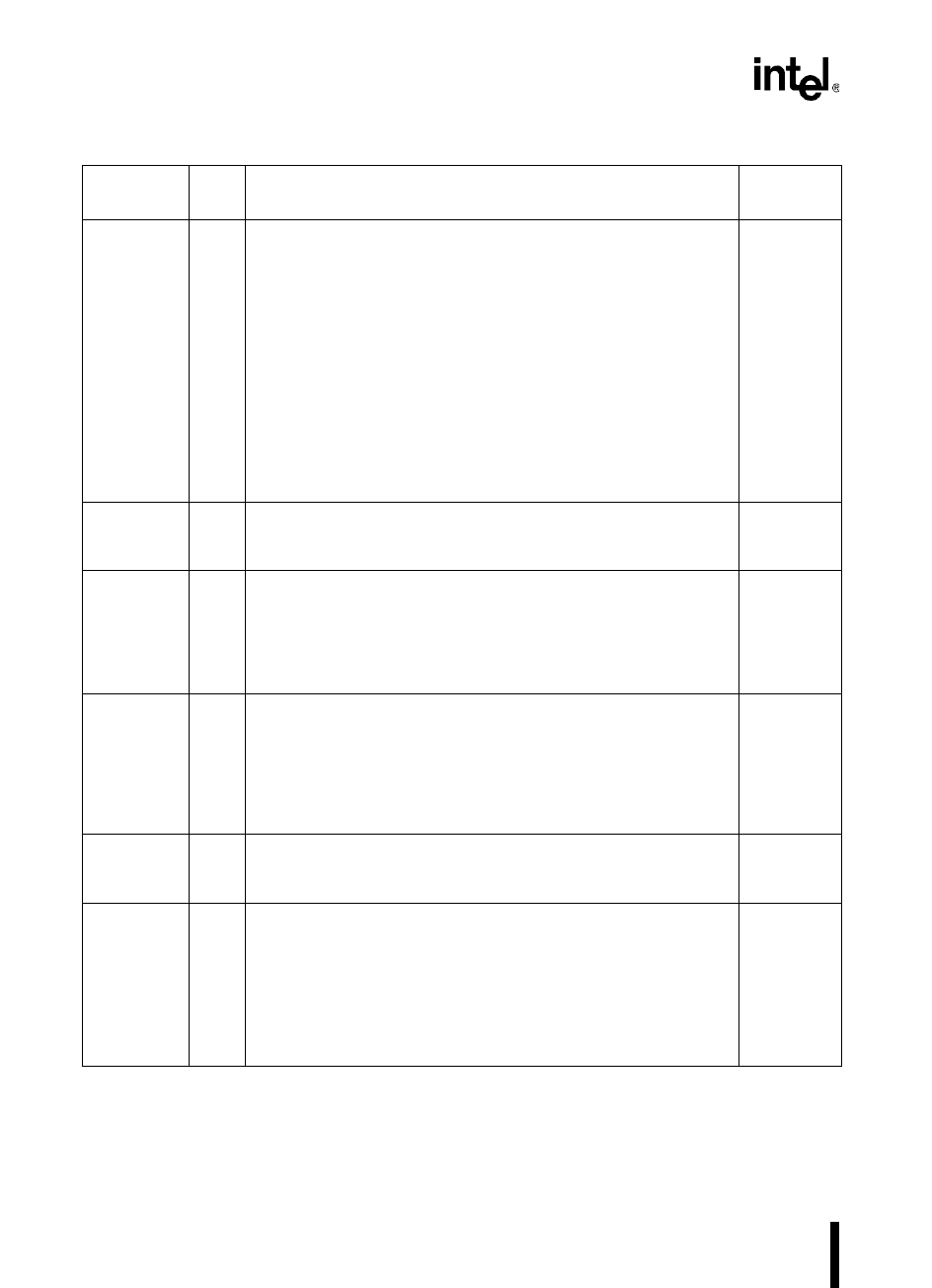

EA# I External Access

This input determines whether memory accesses to special-purpose

and program memory partitions (FF2000–FF2FFFH) are directed to

internal or external memory. These accesses are directed to internal

memory if EA# is held high and to external memory if EA# is held

low. For an access to any other memory location, the value of EA# is

irrelevant.

EA# is not latched and can be switched dynamically during normal

operating mode. Be sure to thoroughly consider the issues, such as

different access times for internal and external memory, before using

this dynamic switching capability.

On devices with no internal nonvolatile memory, always connect EA#

to V

SS

.

EA# is not implemented on the 80C196NU.

—

HLDA# O Bus Hold Acknowledge

This active-low output indicates that the CPU has released the bus

as the result of an external device asserting HOLD#.

P2.6

HOLD# I Bus Hold Request

An external device uses this active-low input signal to request control

of the bus. This pin functions as HOLD# only if the pin is configured

for its special function (see “Bidirectional Port Pin Configurations” on

page 7-7) and the bus-hold protocol is enabled. Setting bit 7 of the

window selection register (WSR) enables the bus-hold protocol.

P2.5

INST O Instruction Fetch

This active-high output signal is valid only during external memory

bus cycles. When high, INST indicates that an instruction is being

fetched from external memory. The signal remains high during the

entire bus cycle of an external instruction fetch. INST is low for data

accesses, including interrupt vector fetches and chip configuration

byte reads. INST is low during internal memory fetches.

—

RD# O Read

Read-signal output to external memory. RD# is asserted only during

external memory reads.

—

READY I Ready Input

This active-high input signal is used to lengthen external memory

cycles for slow memory by generating wait states in addition to the

wait states that are generated internally.

When READY is high, CPU operation continues in a normal manner

with wait states inserted as programmed in CCR0 or the chip-select

x

bus control register. READY is ignored for all internal memory

accesses.

—

Table 13-2. External Memory Interface Signals (Continued)

Name Type Description

Multiplexed

With