8XC196NP, 80C196NU USER’S MANUAL

6-10

6.5 PROGRAMMING THE INTERRUPTS

The PTS select register (PTSSEL) selects either PTS service or a standard software interrupt ser-

vice routine for each of the maskable interrupt requests (see Figure 6-4). The interrupt mask reg-

isters, INT_MASK and INT_MASK1, enable or disable (mask) individual interrupts (see

Figures 6-5 and 6-6). With the exception of the nonmaskable interrupt (NMI) bit

(INT_MASK1.7), setting a bit enables the corresponding interrupt source and clearing a bit dis-

ables the source.

To disable any interrupt, clear its mask bit. To enable an interrupt for standard interrupt service,

set its mask bit and clear its PTS select bit. To enable an interrupt for PTS service, set both the

mask bit and the PTS select bit.

When you assign an interrupt to the PTS, you must set up a PTS control block (PTSCB) for each

interrupt source (see “Initializing the PTS Control Blocks” on page 6-17) and use the EPTS in-

struction to globally enable the PTS. When you assign an interrupt to a standard software service

routine, use the EI (enable interrupts) instruction to globally enable interrupt servicing.

NOTE

The DI (disable interrupts) instruction does not disable PTS service. However,

it does disable service for the end-of-PTS interrupt request. If an interrupt

request occurs while interrupts are disabled, the corresponding pending bit is

set in the INT_PEND or INT_PEND1 register.

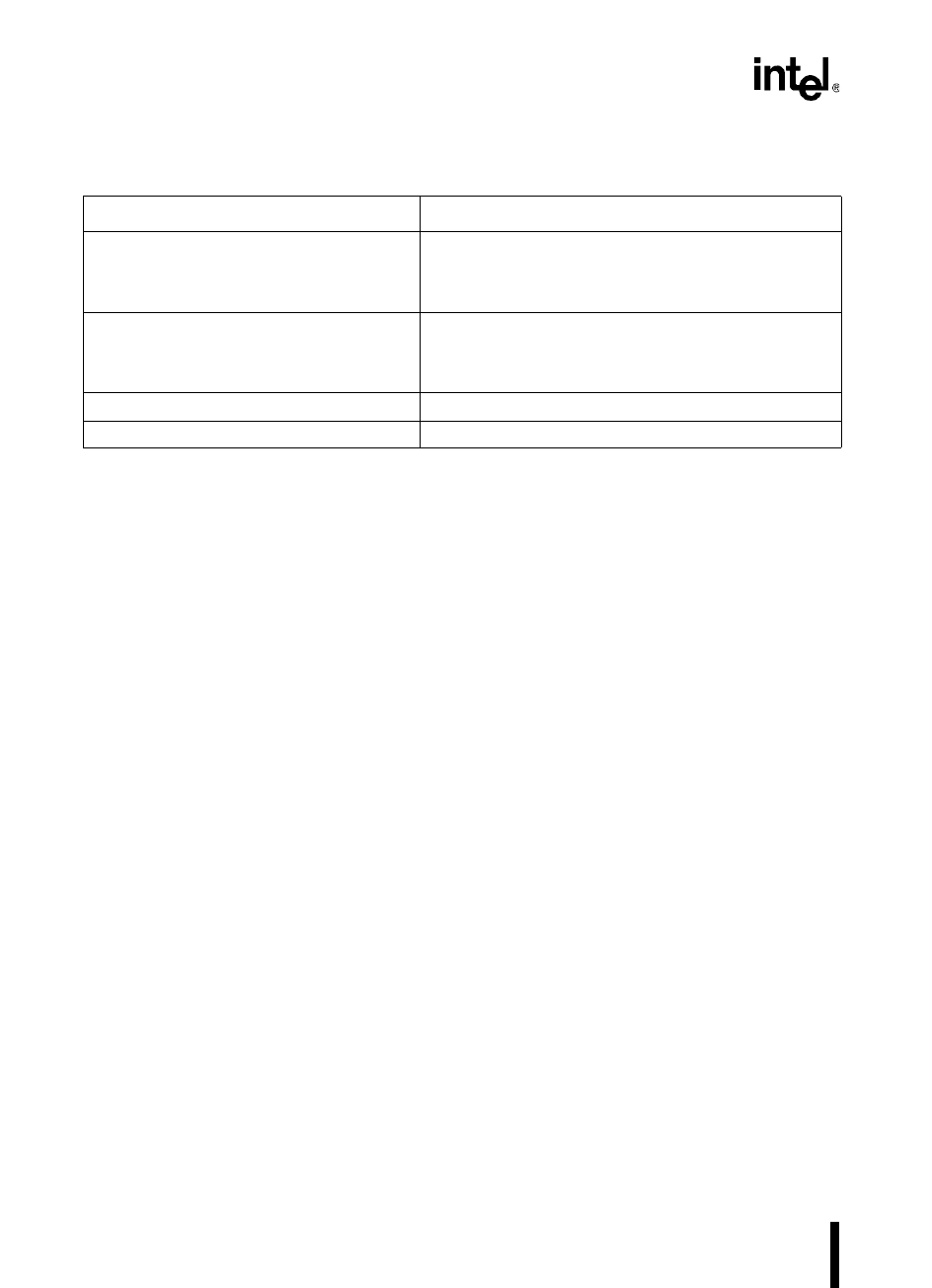

Table 6-4. Execution Times for PTS Cycles

PTS Mode Execution Time (in State Times)

Single transfer mode

register/register

†

memory/register

†

memory/memory

†

18 per byte or word transfer + 1

21 per byte or word transfer + 1

24 per byte or word transfer + 1

Block transfer mode

register/register

†

memory/register

†

memory/memory

†

13 + 7 per byte or word transfer (1 minimum)

16 + 7 per byte or word transfer (1 minimum)

19 + 7 per byte or word transfer (1 minimum)

PWM remap mode 15

PWM toggle mode 15

†

Register

indicates an access to the register file or peripheral SFR.

Memory

indicates an access to a

memory-mapped register, I/O, or memory. See Table 5-1 on page 5-4 for address information.