A-61

INSTRUCTION SET REFERENCE

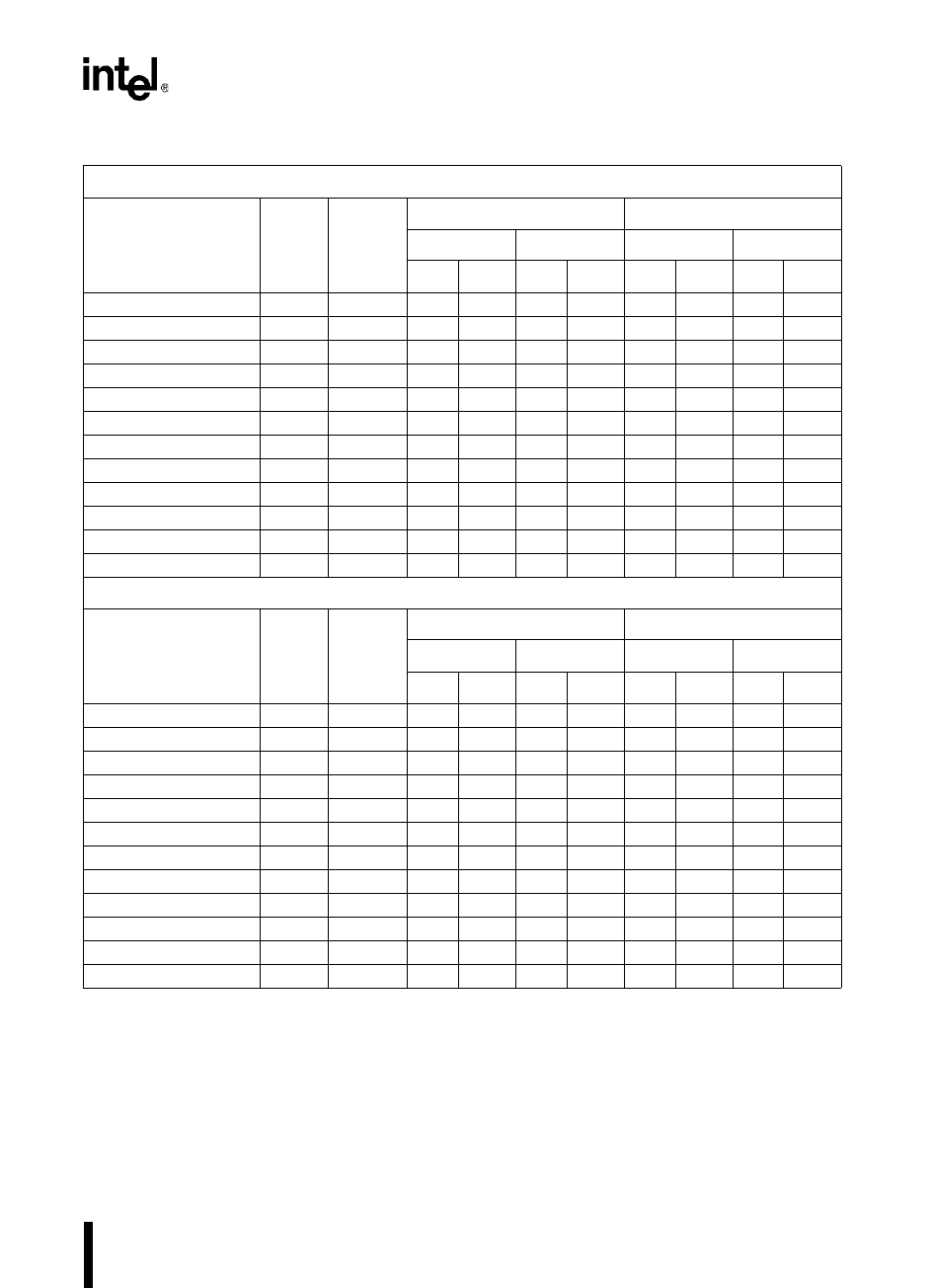

Arithmetic (Group II)

Mnemonic Direct Immed.

Indirect Indexed

Normal Autoinc. Short Long

Reg.Mem.Reg.Mem.Reg.Mem.Reg.Mem.

DIV 26 27 2831293229323033

DIVB 18 18 20 23 21 24 21 24 22 25

DIVU 24 25 26 29 27 30 27 30 28 31

DIVUB 16 16 18 21 19 22 19 22 20 23

MUL (2 ops) 16 17 18 21 19 22 19 22 20 23

MUL (3 ops) 16 17 18 21 19 22 19 22 20 23

MULB (2 ops) 12 12 14 17 15 18 15 18 16 19

MULB (3 ops) 12 12 14 17 15 18 15 18 16 19

MULU (2 ops) 14 15 16 19 17 19 17 20 18 21

MULU (3 ops) 14 15 16 19 17 19 17 20 18 21

MULUB (2 ops) 10 10 12 15 13 15 12 16 14 17

MULUB (3 ops) 10 10 12 15 13 15 12 16 14 17

Logical

Mnemonic Direct Immed.

Indirect Indexed

Normal Autoinc. Short Long

Reg.Mem.Reg.Mem.Reg.Mem.Reg.Mem.

AND (2 ops) 4 5 68796879

AND (3 ops) 5 6 710811710811

ANDB (2 ops) 4 4 68796879

ANDB (3 ops) 5 5 710811710811

NEG 3 — ————————

NEGB 3 — ————————

NOT 3 — ————————

NOTB 3 — ————————

OR 4 5 68796879

ORB 4 4 68796879

XOR 4 5 68796879

XORB 4 4 68796879

Table A-9. Instruction Execution Times (in State Times) (Continued)

NOTE: The column entitled “Reg.” lists the instruction execution times for accesses to the register file or

peripheral SFRs. The column entitled “Mem.” lists the instruction execution times for accesses to

all memory-mapped registers, I/O, or memory. See Table 5-1 on page 5-4 for address information.