7-12

8XC196NP, 80C196NU USER’S MANUAL

7.3.1 EPORT Operation

As Figure 7-2 shows, each EPORT pin serves either as I/O or as an address line, as selected by

the I/O multiplexer. This multiplexer is controlled by the EP_MODE register. If EP_MODE.x is

clear (I/O mode), the pin serves as I/O until EP_MODE.x is changed.

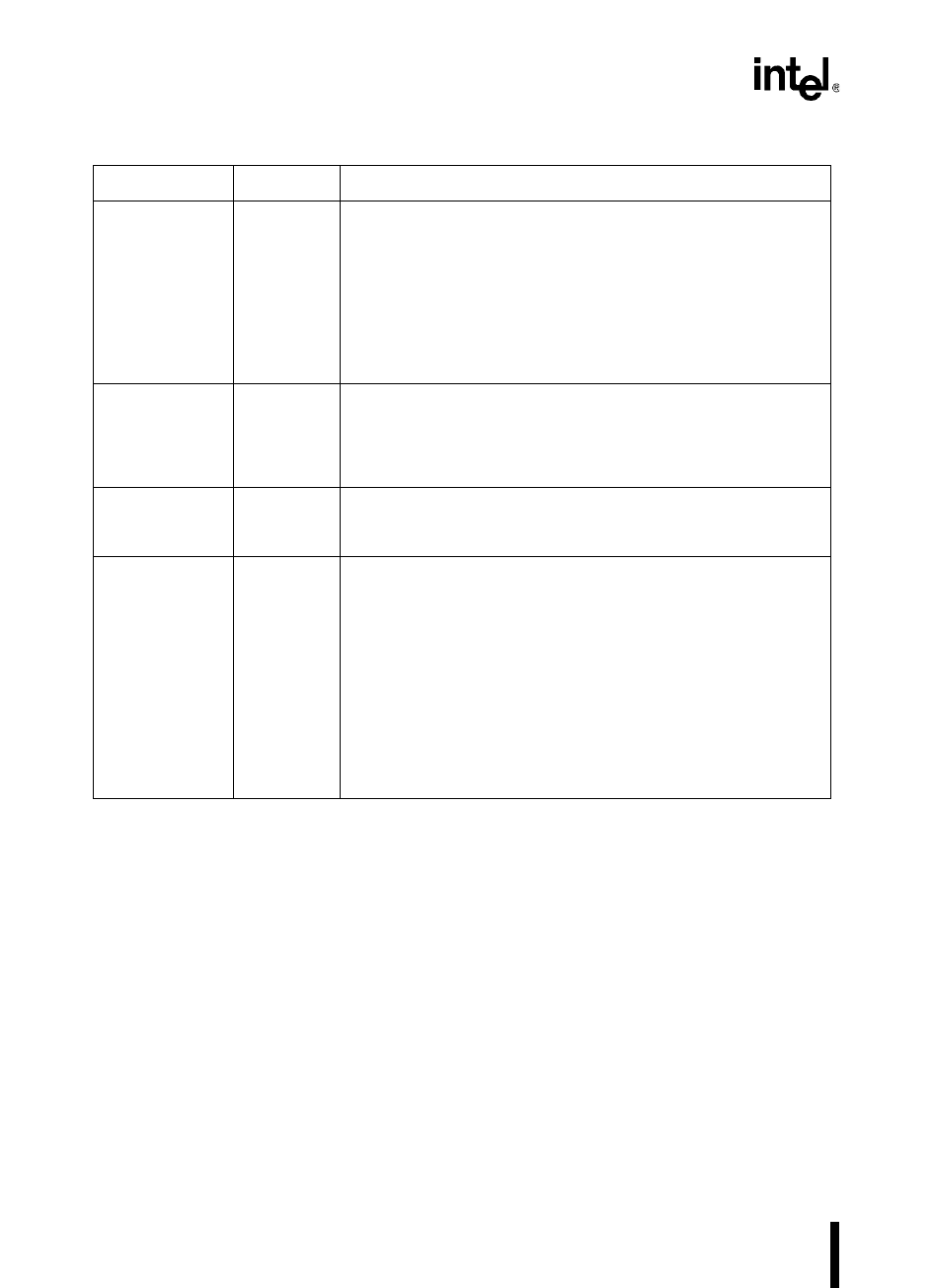

Table 7-10. EPORT Control and Status Registers

Mnemonic Address Description

EP_DIR 1FE3H EPORT Direction

In I/O mode, each bit of EP_DIR controls the direction of the corre-

sponding pin. Clearing a bit configures a pin as a complementary

output; setting a bit configures a pin as either an input or an open-

drain output. (Open-drain outputs require external pull-ups).

Any pin that is configured for its extended-address function is forced

to the complementary output mode except during reset, hold, idle,

powerdown, and standby. (Standby mode is available only on the

80C196NU.)

EP_MODE 1FE1H EPORT Mode

Each bit of EP_MODE controls whether the corresponding pin

functions as a standard I/O port pin or as an extended-address

signal. Setting a bit configures a pin as an extended-address signal;

clearing a bit configures a pin as a standard I/O port pin.

EP_PIN 1FE7H EPORT Pin State

Each bit of EP_PIN reflects the current state of the corresponding

pin, regardless of the pin configuration.

EP_REG 1FE5H EPORT Data Output

Each bit of EP_REG contains data to be driven out by the corre-

sponding pin. When a pin is configured as standard I/O

(EP_MODE.

x

= 0), the result of a CPU write to EP_REG is

immediately visible on the pin.

During nonextended data accesses, EP_REG contains the value of

the memory page that is to be accessed. For compatibility with

software tools, clear the EP_REG bit for any EPORT pin that is

configured as an extended-address signal (EP_MODE.

x

set).

80C196NU Only: For nonextended data accesses, the 80C196NU

forces the page address to 00H. You cannot change pages by

modifying EP_REG.