8XC196NP, 80C196NU USER’S MANUAL

A-54

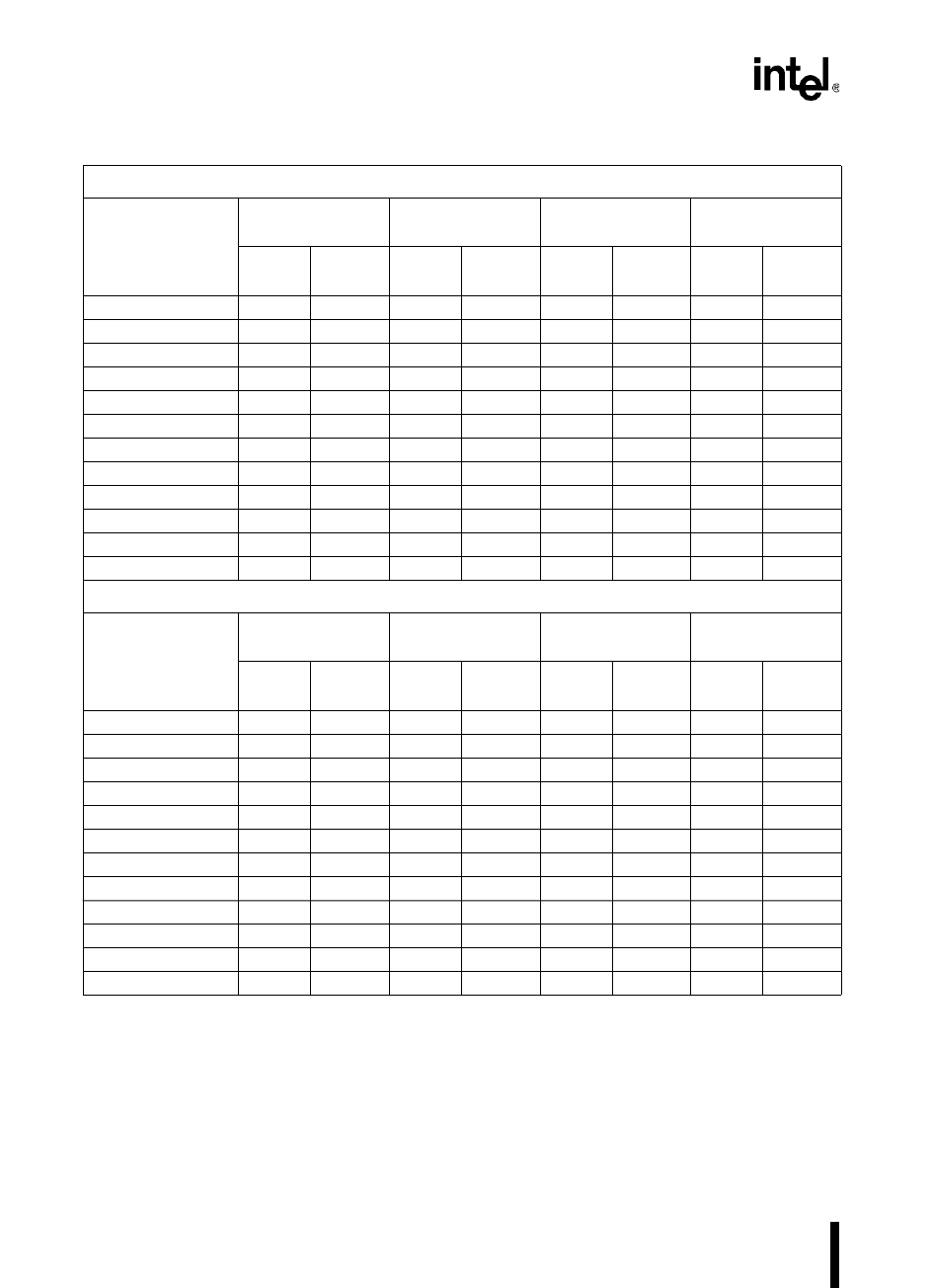

Arithmetic (Group II)

Mnemonic

Direct Immediate

Indirect

(Note 1)

Indexed

(Notes 1, 2)

Length Opcode Length Opcode Length Opcode

Length

S/L

Opcode

DIV 4 FE 8C 5 FE 8D 4 FE 8E 5/6 FE 8F

DIVB 4 FE 9C 4 FE 9D 4 FE 9E 5/6 FE 9F

DIVU 3 8C 4 8D 3 8E 4/5 8F

DIVUB 3 9C 3 9D 3 9E 4/5 9F

MUL (2 ops) 4 FE 6C 5 FE 6D 4 FE 6E 5/6 FE 6F

MUL (3 ops) 5 FE 4C 6 FE 4D 5 FE 4E 6/7 FE 4F

MULB (2 ops) 4 FE 7C 4 FE 7D 4 FE 7E 5/6 FE 7F

MULB (3 ops) 5 FE 5C 5 FE 5D 5 FE 5E 6/7 FE 5F

MULU (2 ops) 3 6C 4 6D 3 6E 4/5 6F

MULU (3 ops) 4 4C 5 4D 4 4E 5/6 4F

MULUB (2 ops) 3 7C 3 7D 3 7E 4/5 7F

MULUB (3 ops) 4 5C 4 5D 4 5E 5/6 5F

Logical

Mnemonic

Direct Immediate

Indirect

(Note 1)

Indexed

(Notes 1, 2)

Length Opcode Length Opcode Length Opcode

Length

S/L

Opcode

AND (2 ops) 3604613624/563

AND (3 ops) 4405414425/643

ANDB (2 ops) 3 70 3 71 3 72 4/5 73

ANDB (3 ops) 4 50 4 51 4 52 5/6 53

NEG 203——————

NEGB 213——————

NOT 202——————

NOTB 212——————

OR 3804813824/583

ORB 3903913924/593

XOR 3844853864/587

XORB 3943953964/597

Table A-8. Instruction Lengths and Hexadecimal Opcodes (Continued)

NOTES:

1. Indirect normal and indirect autoincrement share the same opcodes, as do short- and long-indexed

modes. Because word registers always have even addresses, the address can be expressed in the

upper seven bits; the least-significant bit determines the addressing mode. Indirect normal and short-

indexed modes make the second byte of the instruction even (LSB = 0). Indirect autoincrement and

long-indexed modes make the second byte odd (LSB = 1).

2. For indexed instructions, the first column lists instruction lengths as

S

/

L

, where

S

is the short-indexed

instruction length and

L

is the long-indexed instruction length.

3. For the SCALL and SJMP instructions, the three least-significant bits of the opcode are concatenated

with the eight bits to form an 11-bit, 2’s complement offset.