8XC196NP, 80C196NU USER’S MANUAL

13-30

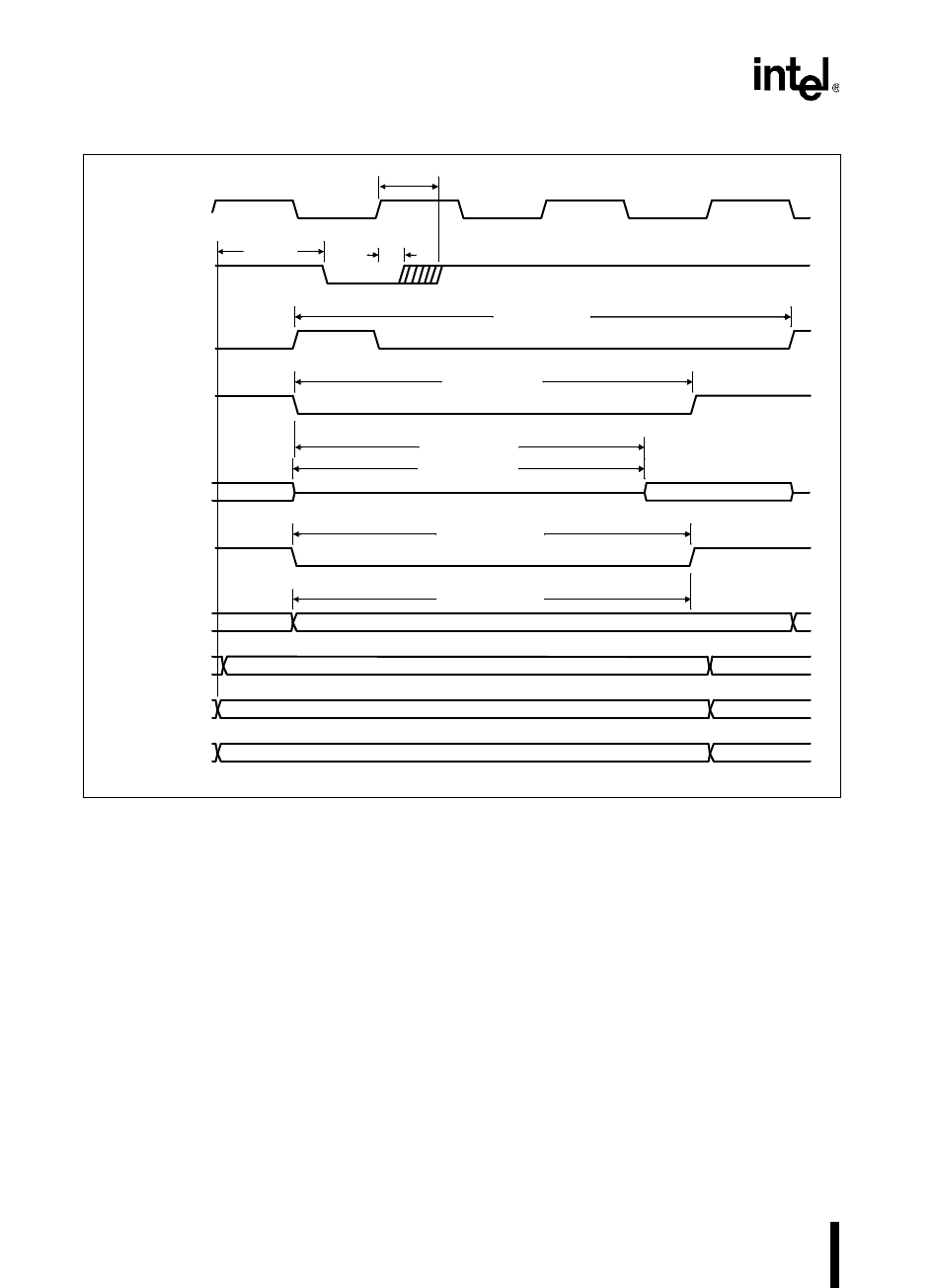

Figure 13-15. READY Timing Diagram — Demultiplexed Mode (80C196NU)

13.7 BUS-HOLD PROTOCOL

The 8XC196Nx supports a bus-hold protocol that allows external devices to gain control of the

address/data bus. The protocol uses three signals, all of which are port 2 special functions:

HOLD#/P2.5 (bus-hold request), HLDA#/P2.6 (bus-hold acknowledge), and BREQ#/P2.3 (bus

request). When an external device wants to use the 8XC196Nx bus, it asserts the HOLD# signal.

HOLD# is sampled while CLKOUT is low. The 8XC196Nx responds by releasing the bus and

asserting HLDA#. During this hold time, the address/data bus floats, and signals CSx#, ALE,

RD#, WR#/WRL#, BHE#/WRH#, and INST are weakly held in their inactive states. Figure

13-16 shows the timing for bus-hold protocol, and Table 13-12 on page 13-31 lists the timing pa-

rameters and their definitions. Refer to the datasheet for timing parameter values.

T0014-02

T

CHYX

(max)

T

WLWH

+ 2t

T

AVYV

T

LHLH

+ 2t

T

RLRH

+ 2t

T

AVDV

+ 2t

T

RLDV

+ 2t

T

QVWH

+ 2t

Data Valid

Data Valid

CLKOUT

READY

ALE

RD#

AD15:0

WR#

AD15:0

BHE#, INST

A19:16

CS

x

#

T

CHYX

(min)

(read)

(write)