8XC196NP, 80C196NU USER’S MANUAL

13-40

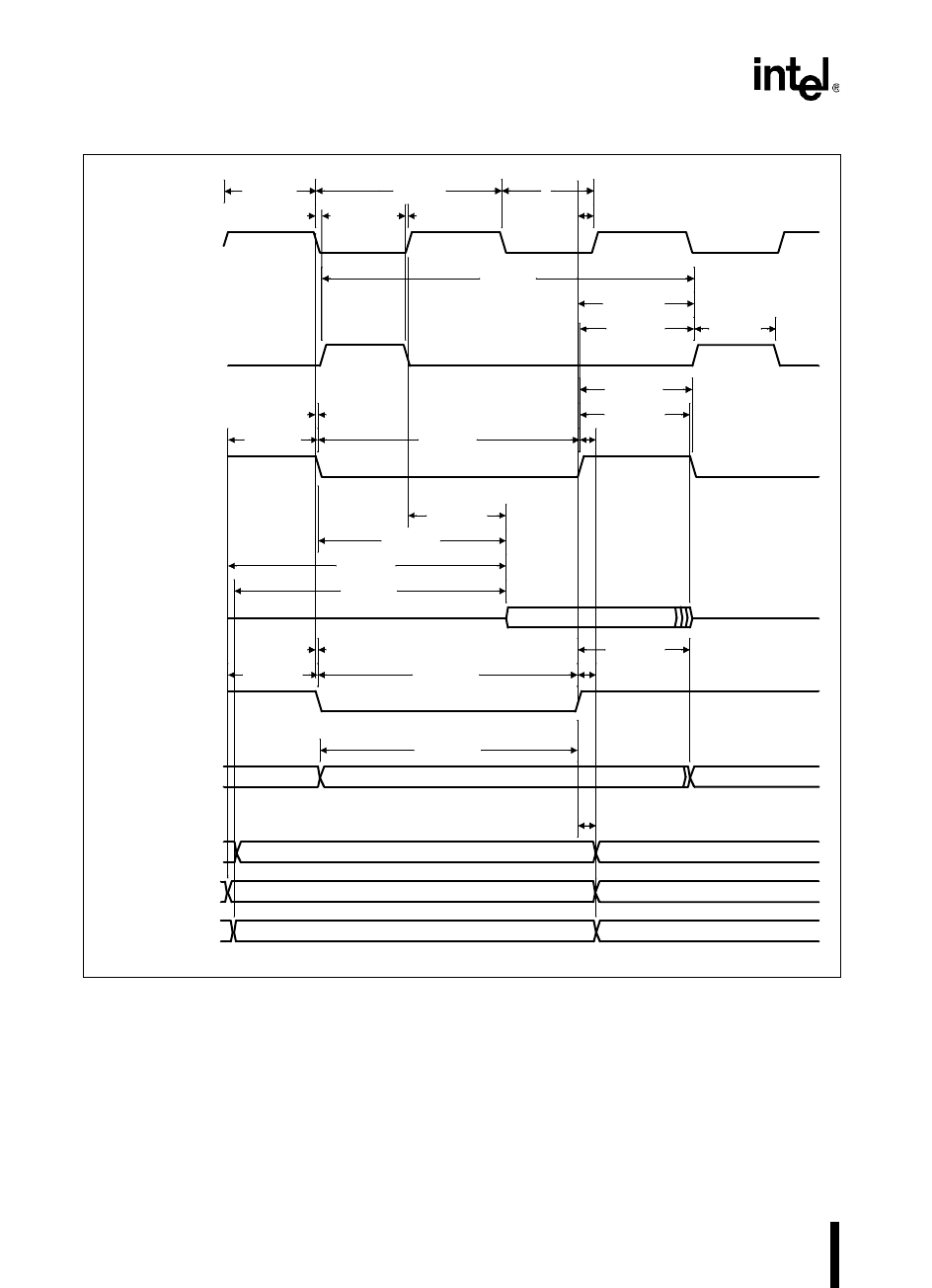

Figure 13-23. Demultiplexed System Bus Timing (80C196NU)

13.9.1 Deferred Bus-cycle Mode (80C196NU Only)

The 80C196NU offers a deferred bus cycle mode. This bus mode (enabled by CCR1.5; see Figure

13-7 on page 13-16) reduces bus contention when using the 80C196NU in demultiplexed mode

with slow memories. As shown in Figure 13-24, a delay of 2t occurs in the first bus cycle follow-

ing a chip-select output change and the first write cycle following a read cycle.

T0012-02

T

CLCL

T

CHWH

T

LLCH

T

LHLH

T

WHLH

T

AVRL

T

RHRL

T

RHAX

T

RHDZ

T

AVWL

T

WLWH

T

WHAX

T

QVWH

T

WHBX

,T

RHBX

T

CLLH

T

T

LHLL

T

RHLH

T

RLRH

T

RLCL

T

SLDV

T

AVDV

T

RLDV

T

CHDV

T

WLCL

T

WHQX

Valid

Valid

CLKOUT

ALE

RD#

AD15:0

WR#

AD15:0

BHE#, INST

A19:0

CS

x

#

T

CHCL

(read)

(write)