6-11

STANDARD AND PTS INTERRUPTS

6.5.1 Programming Considerations for Multiplexed Interrupts

An overrun on the EPA capture compare channels can generate the multiplexed capture overrun

interrupts (OVR0_1 and OVR2_3). Write to the EPA_MASK (Figure 10-11 on page 10-22) reg-

ister to enable or disable the multiplexed interrupt sources and the INT_MASK1 register to en-

able or disable the OVR0_1 and OVR2_3 interrupts.

PTS service is not recommended for multiplexed interrupts because it cannot determine the inter-

rupt source.

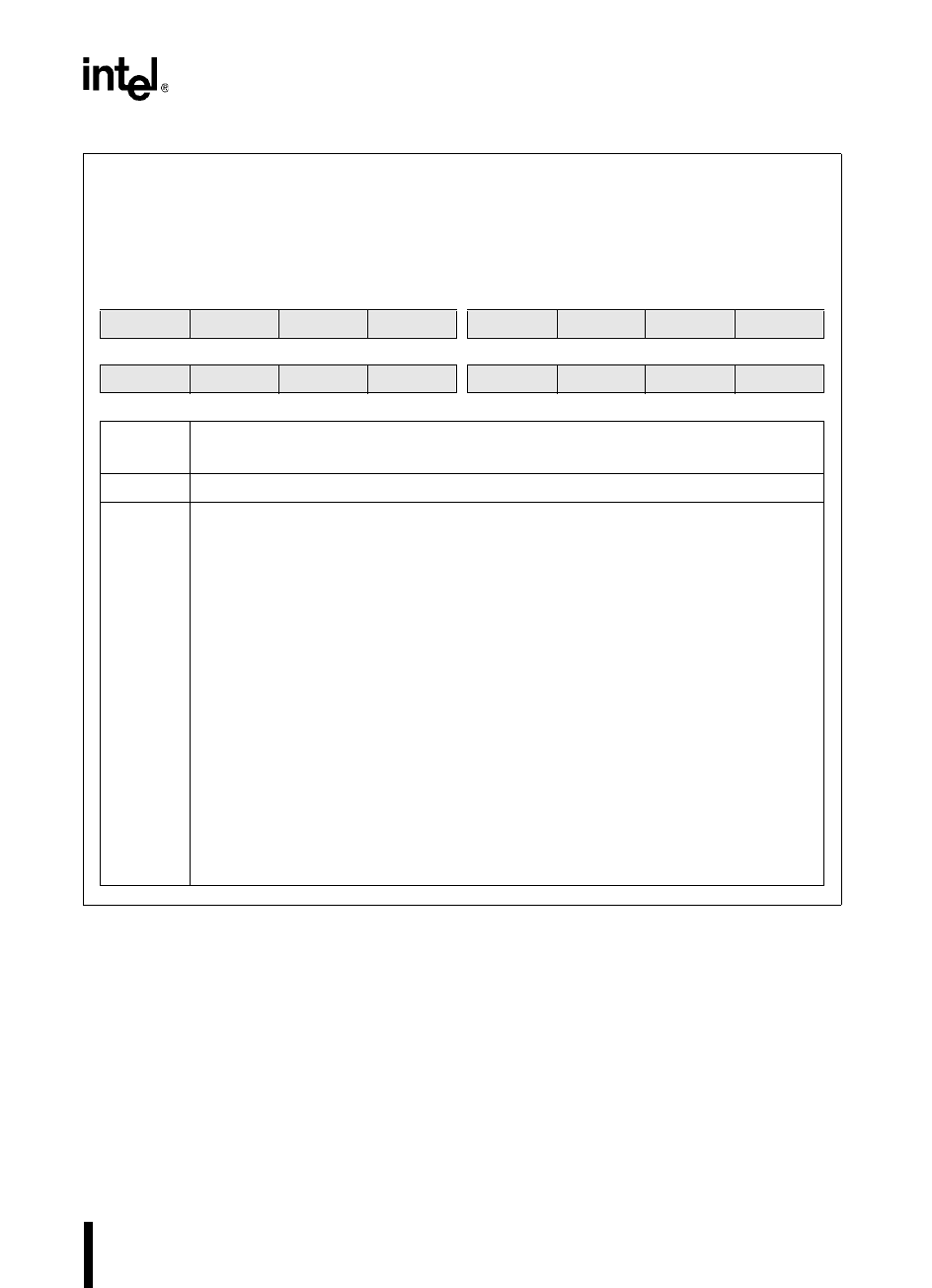

PTSSEL

Address:

Reset State:

0004H

0000H

The PTS select (PTSSEL) register selects either a PTS microcode routine or a standard interrupt

service routine for each interrupt request. Setting a bit selects a PTS microcode routine; clearing a bit

selects a standard interrupt service routine. When PTSCOUNT reaches zero, hardware clears the

corresponding PTSSEL bit. The PTSSEL bit must be set manually to re-enable the PTS channel.

15 8

— EXTINT3 EXTINT2 OVR2_3 OVR0_1 EPA3 EPA2 EPA1

7 0

EPA0 RI TI EXTINT1 EXTINT0 — OVRTM2 OVRTM1

Bit

Number

Function

15, 2 Reserved; for compatibility with future devices, write zero to this bit.

14:3

1:0

Setting a bit causes the corresponding interrupt to be handled by a PTS microcode

routine.

The PTS interrupt vector locations are as follows:

Bit Mnemonic Interrupt PTS Vector

EXTINT3 EXTINT3 pin FF205CH

EXTINT2 EXTINT2 pin FF205AH

OVR2_3

†

EPA Capture Channel 2 or 3 Overrun FF2058H

OVR0_1

†

EPA Capture Channel 0 or 1 Overrun FF2056H

EPA3 EPA Capture/Compare Channel 3 FF2054H

EPA2 EPA Capture/Compare Channel 2 FF2052H

EPA1 EPA Capture/Compare Channel 1 FF2050H

EPA0 EPA Capture/Compare Channel 0 FF204EH

RI SIO Receive FF204CH

TI SIO Transmit FF204AH

EXTINT1 EXTINT1 pin FF2048H

EXTINT0 EXTINT0 pin FF2046H

OVRTM2 Timer 2 Overflow/ Underflow FF2042H

OVRTM1 Timer 1 Overflow/ Underflow FF2040H

†

PTS service is not recommended because the PTS cannot determine the source of

shared interrupts.

Figure 6-4. PTS Select (PTSSEL) Register