7-1

CHAPTER 7

I/O PORTS

I/O ports provide a mechanism to transfer information between the device and the surrounding

system circuitry. They can read system status, monitor system operation, output device status,

configure system options, generate control signals, provide serial communication, and so on.

Their usefulness in an application is limited only by the number of I/O pins available and the

imagination of the engineer.

7.1 I/O PORTS OVERVIEW

Standard I/O port registers are located in the SFR address space and they can be windowed. Mem-

ory-mapped I/O port registers are located in memory-mapped address space. Memory-mapped

registers must be accessed with indirect or indexed addressing; they cannot be windowed. All

ports can provide low-speed input/output pins or serve alternate functions. Table 7-1 provides an

overview of the device I/O ports. The remainder of this chapter describes the ports in more detail

and explains how to configure the pins. The chapters that cover the associated peripherals discuss

using the pins for their special functions.

7.2 BIDIRECTIONAL PORTS 1–4

The bidirectional ports are very similar in both circuitry and configuration. All ports use Schmitt-

triggered input buffers for improved noise immunity. Table 7-2 lists the bidirectional port pins

with their special-function signals and associated peripherals.

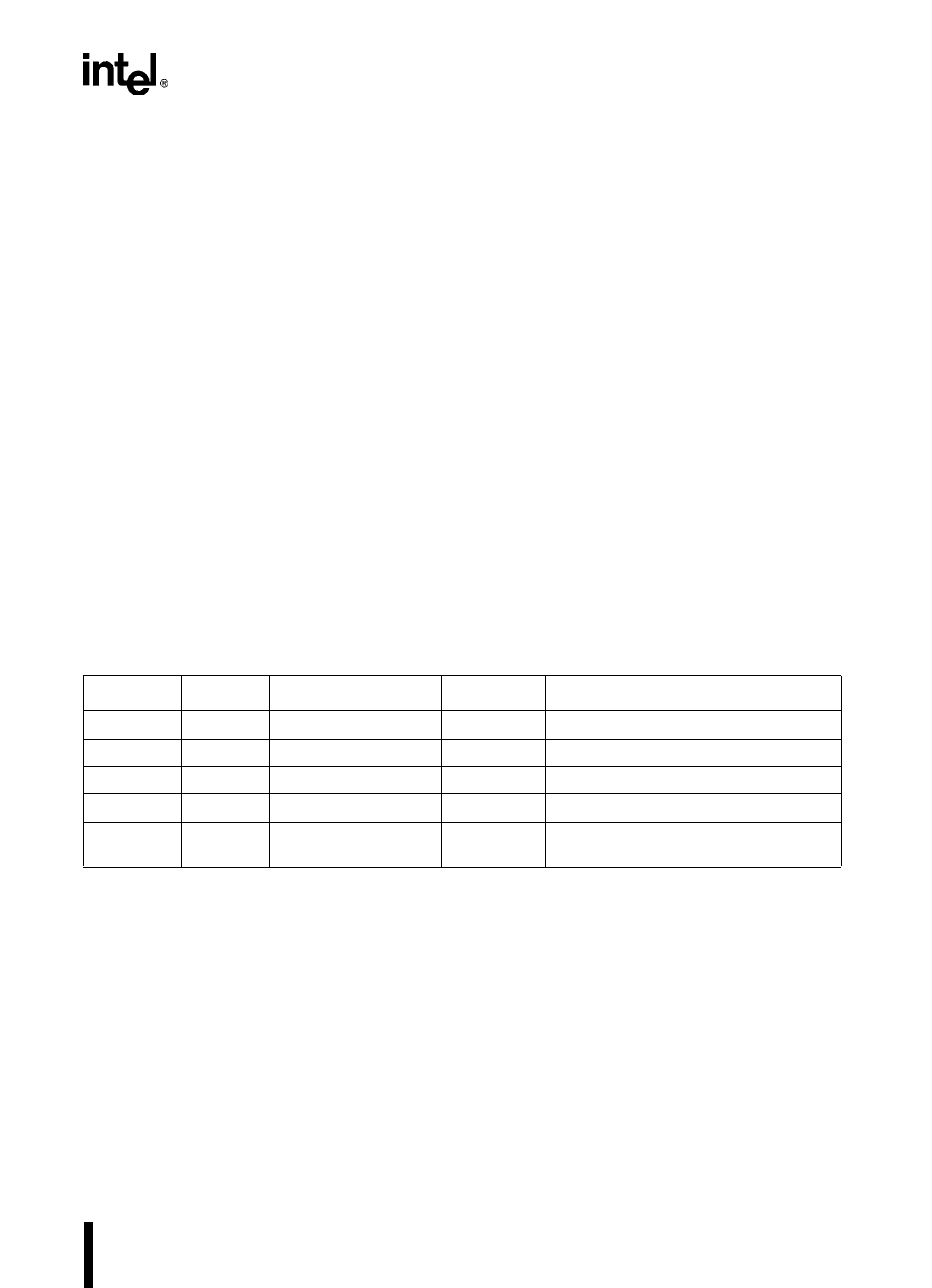

Table 7-1. Device I/O Ports

Port Bits Type Direction Associated Peripheral(s)

Port 1 8 Standard Bidirectional EPA and timers

Port 2 8 Standard Bidirectional SIO, interrupts, bus control, clock gen.

Port 3 8 Standard Bidirectional Chip-select unit, interrupts

Port 4 4 Standard Bidirectional PWM

EPORT 4

Memory mapped (NP)

Standard (NU)

Bidirectional Extended address lines