12-2

8XC196NP, 80C196NU USER’S MANUAL

— PLLEN2:1

(80C196NU

only)

I Phase Lock Loop 1 and 2 Enable

These input pins are used to enable the on-chip clock multiplier

feature and select either the doubled or quadrupled clock speed.

CAUTION: If PLLEN1 is held low while PLLEN2 is held high, the

device will enter into an unsupported test mode.

— RESET# I/O Reset

A level-sensitive reset input to and open-drain system reset output

from the microcontroller. Either a falling edge on RESET# or an

internal reset turns on a pull-down transistor connected to the

RESET# pin for 16 state times. In the powerdown, standby, and idle

modes, asserting RESET# causes the chip to reset and return to

normal operating mode. After a device reset, the first instruction fetch

is from FF2080H (or F2080H in external memory). For the 80C196NP

and 80C196NU, the program and special-purpose memory locations

(FF2000–FF2FFFH) reside in external memory. For the 83C196NP,

these locations can reside either in external memory or in internal

ROM.

— RPD I Return from Powerdown

Timing pin for the return-from-powerdown circuit.

If your application uses powerdown mode, connect a capacitor

†

between RPD and V

SS

if either of the following conditions is true.

• the internal oscillator is the clock source

• the phase-locked loop (PLL) circuitry (80C196NU only) is

enabled (see PLLEN2:1 signal description)

The capacitor causes a delay that enables the oscillator and PLL

circuitry to stabilize before the internal CPU and peripheral clocks are

enabled.

The capacitor is not required if your application uses powerdown

mode and if both of the following conditions are true.

• an external clock input is the clock source

• the phase-locked loop circuitry (80C196NU only) is disabled

If your application does not use powerdown mode, leave this pin

unconnected.

†

Calculate the value of the capacitor using the formula found on page

12-11.

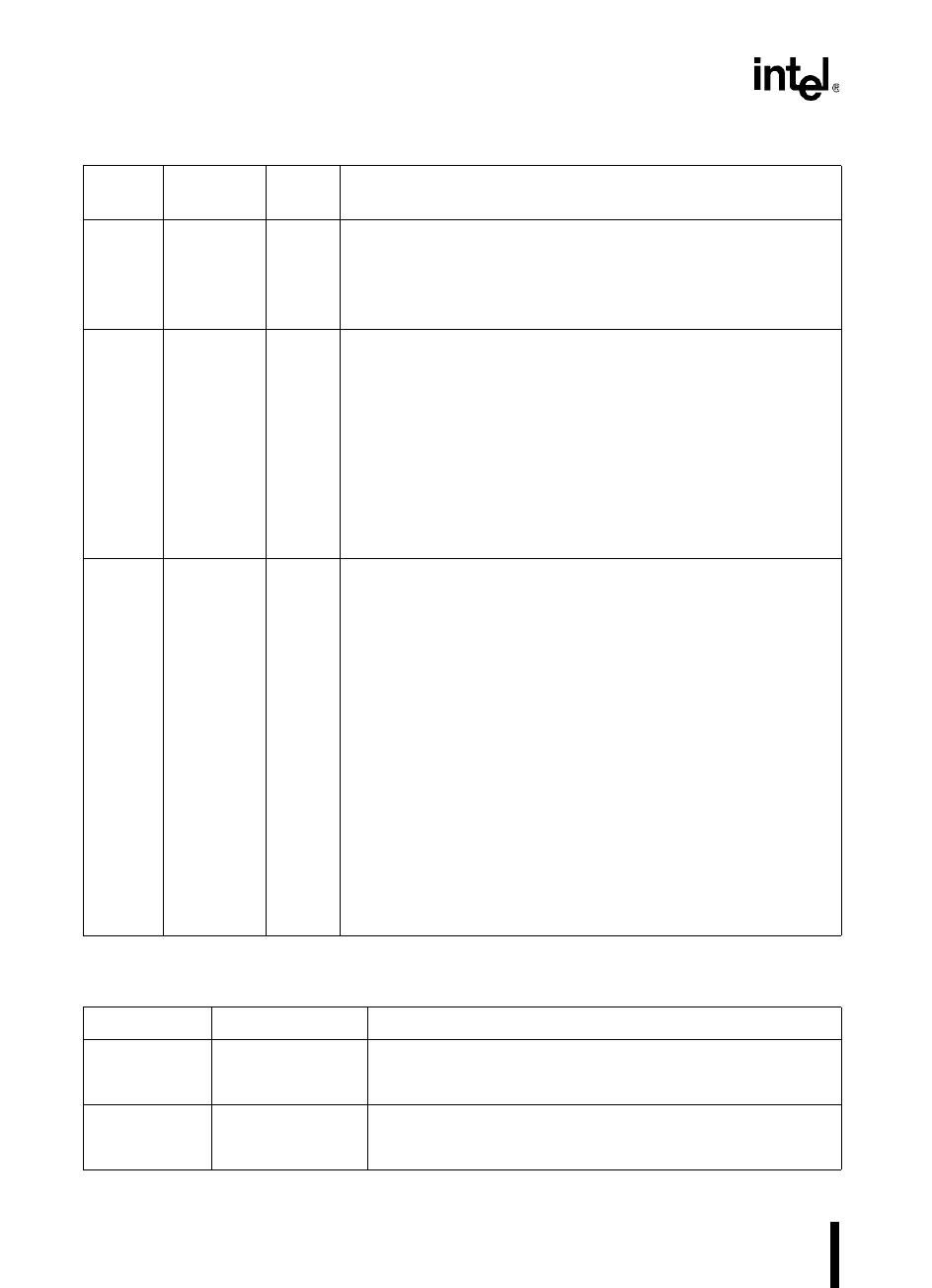

Table 12-2. Operating Mode Control and Status Registers

Mnemonic Address Description

CCR0 2018H Chip Configuration 0 Register

Bit 0 of this register enables and disables standby and

powerdown mode.

INT_MASK 0008H Interrupt Mask

Bits 3 and 4 of this register enable and disable (mask) the

external interrupts, EXTINT0 and EXTINT1.

Table 12-1. Operating Mode Control Signals (Continued)

Port Pin

Signal

Name

Type Description