6-5

STANDARD AND PTS INTERRUPTS

6.3.1.1 Unimplemented Opcode

If the CPU attempts to execute an unimplemented opcode, an indirect vector through location

FF2012H occurs. This prevents random software execution during hardware and software fail-

ures. The interrupt vector should contain the starting address of an error routine that will not fur-

ther corrupt an already erroneous situation. The unimplemented opcode interrupt prevents other

interrupt requests from being acknowledged until after the next instruction is executed.

6.3.1.2 Software Trap

The TRAP instruction (opcode F7H) causes an interrupt call that is vectored through location

FF2010H. The TRAP instruction provides a single-instruction interrupt that is useful when de-

bugging software or generating software interrupts. The TRAP instruction prevents other inter-

rupt requests from being acknowledged until after the next instruction is executed.

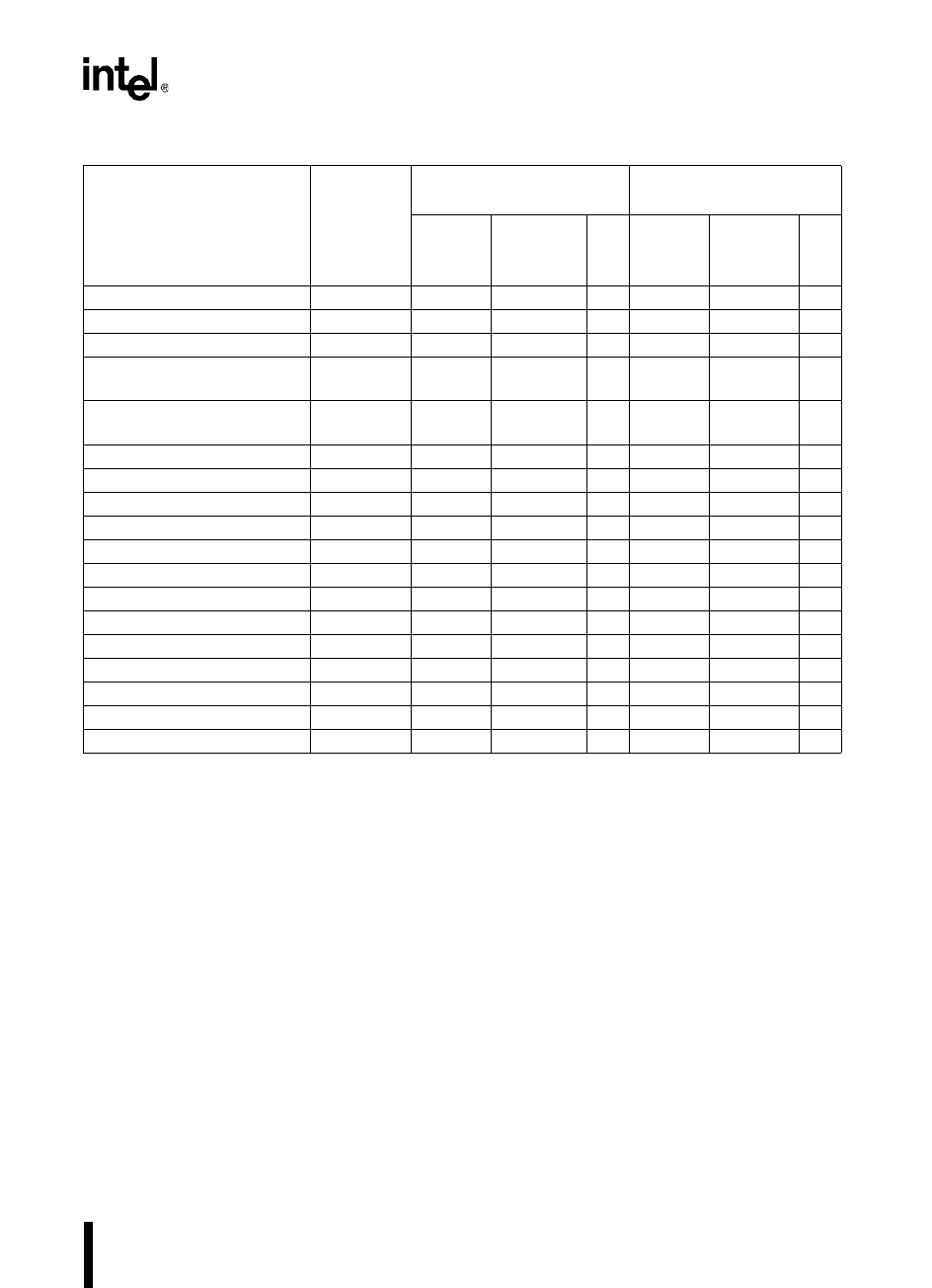

Table 6-3. Interrupt Sources, Vectors, and Priorities

Interrupt Source Mnemonic

Interrupt Controller

Service

PTS Service

Name

Vector

Priority

Name

Vector

Priority

Nonmaskable Interrupt NMI INT15 FF203EH 30 — — —

EXTINT3 Pin EXTINT3 INT14 FF203CH 14 PTS14 FF205CH 29

EXTINT2 Pin EXTINT2 INT13 FF203AH 13 PTS13 FF205AH 28

EPA capture overrun in

channel 2 or 3

OVR2_3

†

INT12 FF2038H 12 PTS12 FF2058H 27

EPA capture overrun in

channel 0 or 1

OVR0_1

†

INT11 FF2036H 11 PTS11 FF2056H 26

EPA Capture/Compare 3 EPA3 INT10 FF2034H 10 PTS10 FF2054H 25

EPA Capture/Compare 2 EPA2 INT09 FF2032H 09 PTS09 FF2052H 24

EPA Capture/Compare 1 EPA1 INT08 FF2030H 08 PTS08 FF2050H 23

Unimplemented Opcode — — FF2012H — — — —

Software TRAP Instruction — — 0FF2010H — — — —

EPA Capture/Compare 0 EPA0 INT07 FF200EH 07 PTS07 FF204EH 22

SIO Receive RI INT06 FF200CH 06 PTS06 FF204CH 21

SIO Transmit TI INT05 FF200AH 05 PTS05 FF204AH 20

EXTINT1 Pin EXTINT1 INT04 FF2008H 04 PTS04 FF2048H 19

EXTINT0 Pin EXTINT0 INT03 FF2006H 03 PTS03 FF2046H 18

Reserved Reserved INT02 FF2004H 02 PTS02 FF2044H 17

Timer 2 Overflow OVRTM2 INT01 FF2002H 01 PTS01 FF2042H 16

Timer 1 Overflow OVRTM1 INT00 FF2000H 00 PTS00 FF2040H 15

†

PTS service is not recommended because the PTS cannot determine the source of shared interrupts.