A-53

INSTRUCTION SET REFERENCE

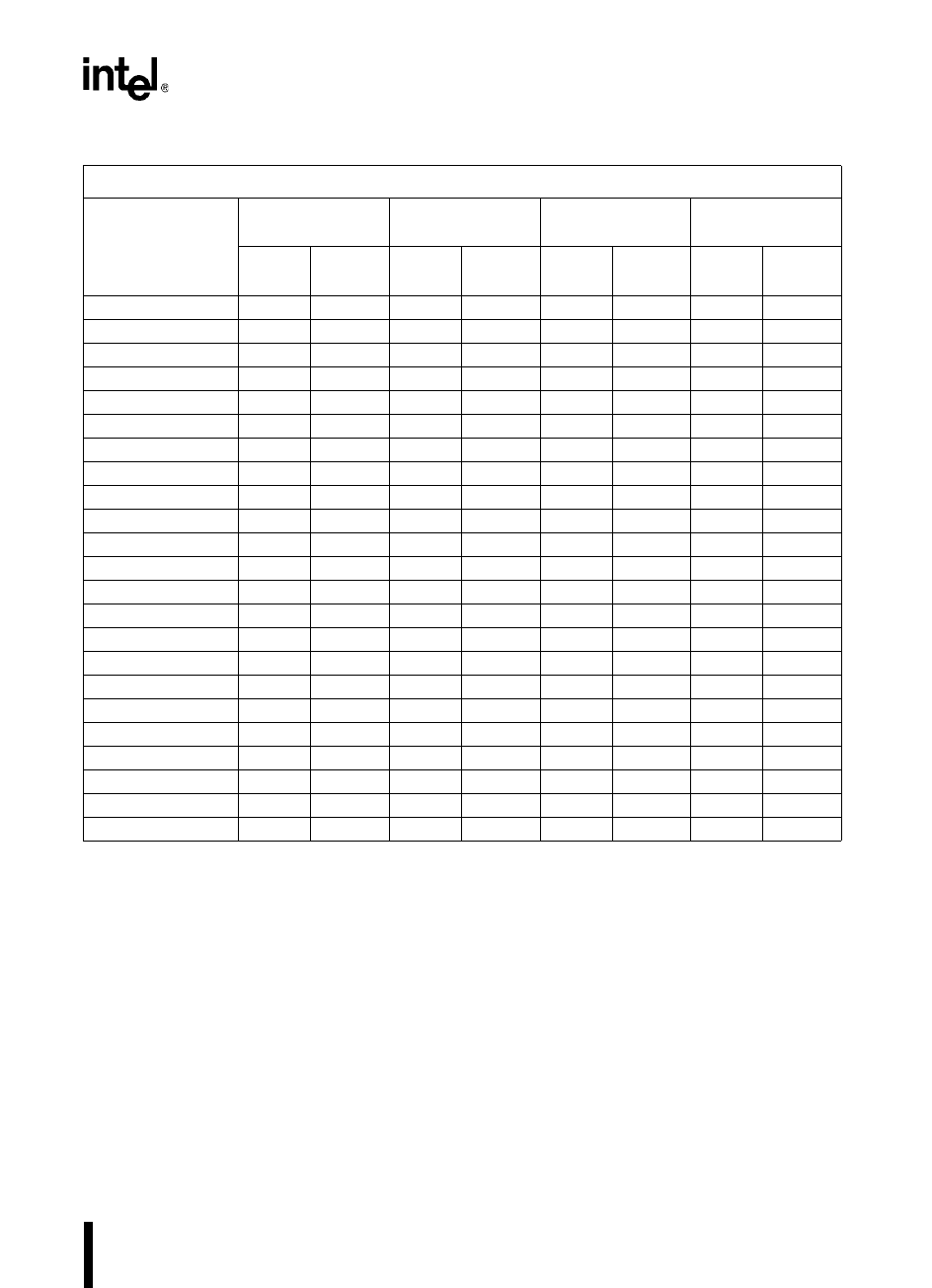

Table A-8. Instruction Lengths and Hexadecimal Opcodes

Arithmetic (Group I)

Mnemonic

Direct Immediate

Indirect

(Note 1)

Indexed

(Notes 1, 2)

Length Opcode Length Opcode Length Opcode

Length

S/L

Opcode

ADD (2 ops) 3644653664/567

ADD (3 ops) 4445454465/647

ADDB (2 ops) 3 74 3 75 3 76 4/5 77

ADDB (3 ops) 4 54 4 55 4 56 5/6 57

ADDC 3A44A53A64/5A7

ADDCB 3 B4 3 B5 3 B6 4/5 B7

CLR 201——————

CLRB 211——————

CMP 38848938A4/58B

CMPB 39839939A4/59B

CMPL 3C5——————

DEC 205——————

DECB 215——————

EXT 206——————

EXTB 216——————

INC 207——————

INCB 217——————

SUB (2 ops) 3 68 4 69 3 6A 4/5 6B

SUB (3 ops) 4 48 5 49 4 4A 5/6 4B

SUBB (2 ops) 3 78 3 79 3 7A 4/5 7B

SUBB (3 ops) 4 58 4 59 4 5A 5/6 5B

SUBC 3 A8 4 A9 3 AA 4/5 AB

SUBCB 3 B8 3 B9 3 BA 4/5 BB

NOTES:

1. Indirect normal and indirect autoincrement share the same opcodes, as do short- and long-indexed

modes. Because word registers always have even addresses, the address can be expressed in the

upper seven bits; the least-significant bit determines the addressing mode. Indirect normal and short-

indexed modes make the second byte of the instruction even (LSB = 0). Indirect autoincrement and

long-indexed modes make the second byte odd (LSB = 1).

2. For indexed instructions, the first column lists instruction lengths as

S

/

L

, where

S

is the short-indexed

instruction length and

L

is the long-indexed instruction length.

3. For the SCALL and SJMP instructions, the three least-significant bits of the opcode are concatenated

with the eight bits to form an 11-bit, 2’s complement offset.