C-49

REGISTERS

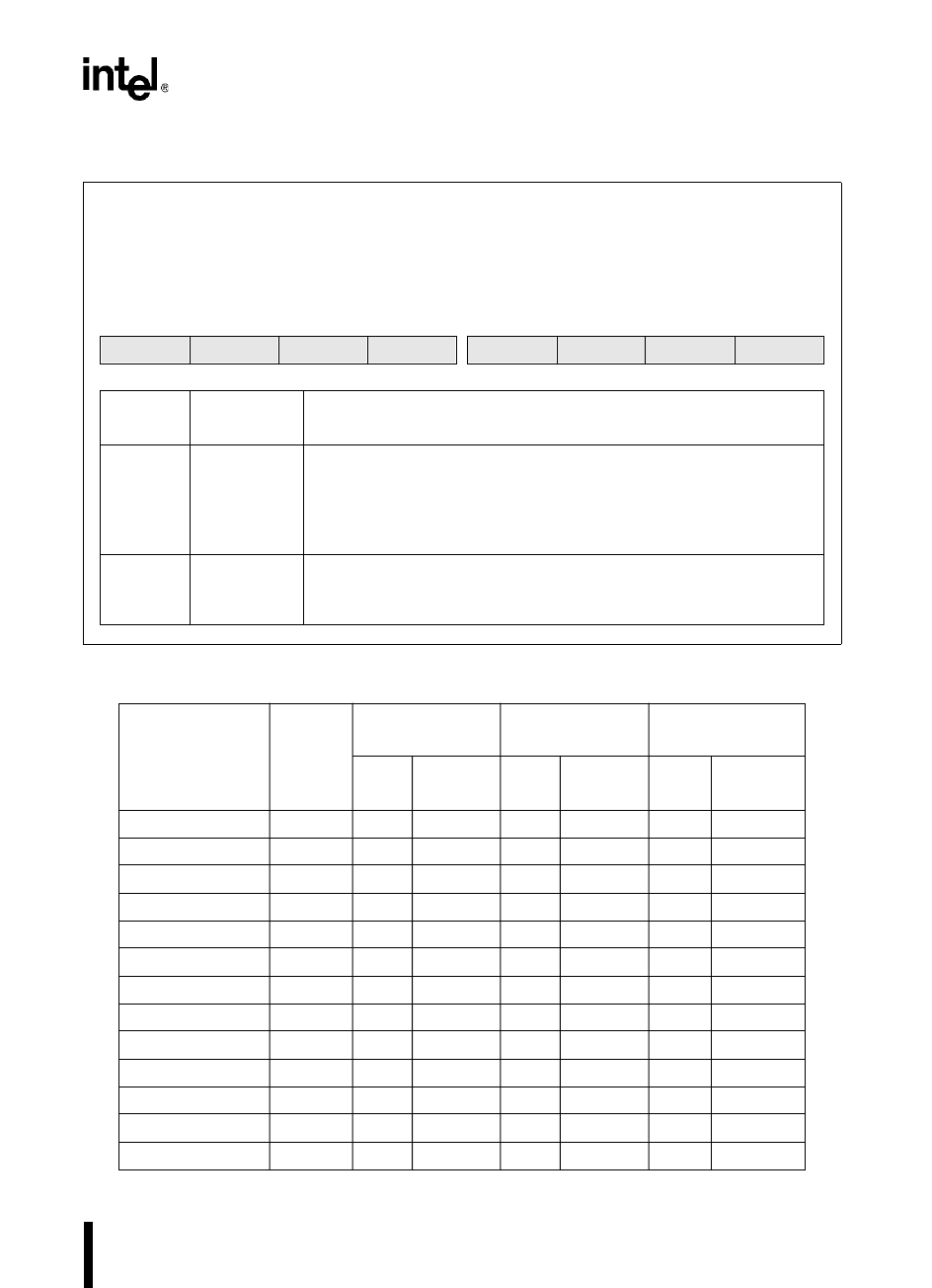

WSR

WSR

Address:

Reset State:

0014H

00H

The window selection register (WSR) has two functions. One bit enables and disables the bus-hold

protocol. The remaining bits select windows. Windows map sections of RAM into the top of the lower

register file, in 32-, 64-, or 128-byte increments. PUSHA saves this register on the stack and POPA

restores it.

7 0

HLDEN W6 W5 W4 W3 W2 W1 W0

Bit

Number

Bit

Mnemonic

Function

7 HLDEN HOLD#, HLDA# Protocol Enable

This bit enables and disables the bus-hold protocol (see Chapter 13,

“Interfacing with External Memory”). It has no effect on windowing.

1 = enable

0 = disable

6:0 W6:0 Window Selection

These bits specify the window size and window number. See Table 5-8

on page 5-15 or Table 5-9 on page 5-15.

Table C-18. WSR Settings and Direct Addresses for Windowable SFRs

Register

Mnemonic

Memory

Location

32-byte Windows

(00E0–00FFH)

64-byte Windows

(00C0–00FFH)

128-byte Windows

(0080–00FFH)

WSR

Direct

Address

WSR

Direct

Address

WSR

Direct

Address

ADDRCOM0

†

1F40H 7AH 00E0H 3DH 00C0H 1EH 00C0H

ADDRCOM1

†

1F48H 7AH 00E8H 3DH 00C8H 1EH 00C8H

ADDRCOM2

†

1F50H 7AH 00F0H 3DH 00D0H 1EH 00D0H

ADDRCOM3

†

1F58H 7AH 00F8H 3DH 00D8H 1EH 00D8H

ADDRCOM4

†

1F60H 7BH 00E0H 3DH 00E0H 1EH 00E0H

ADDRCOM5

†

1F68H 7BH 00E8H 3DH 00E8H 1EH 00E8H

ADDRMSK0

†

1F42H 7AH 00E2H 3DH 00C2H 1EH 00C2H

ADDRMSK1

†

1F4AH 7AH 00EAH 3DH 00CAH 1EH 00CAH

ADDRMSK2

†

1F52H 7AH 00F2H 3DH 00D2H 1EH 00D2H

ADDRMSK3

†

1F5AH 7AH 00FAH 3DH 00DAH 1EH 00DAH

ADDRMSK4

†

1F62H 7BH 00E2H 3DH 00E2H 1EH 00E2H

ADDRMSK5

†

1F6AH 7BH 00EAH 3DH 00EAH 1EH 00EAH

BUSCON0 1F44H 7AH 00E4H 3DH 00C4H 1EH 00C4H

†

Must be addressed as a word.