8XC196NP, 80C196NU USER’S MANUAL

A-66

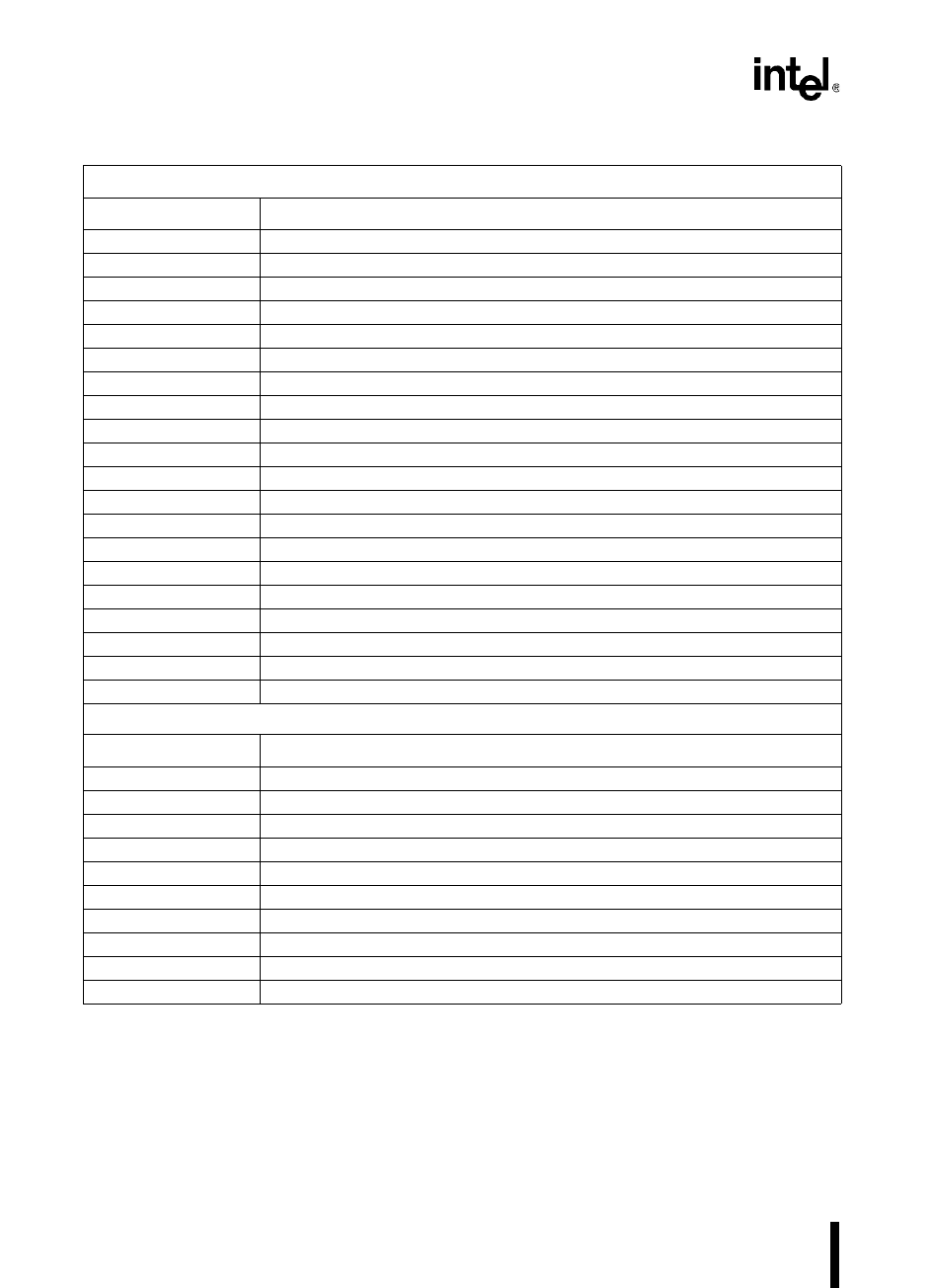

Conditional Jump

Mnemonic Short-Indexed

DJNZ 5 (jump not taken), 9 (jump taken)

DJNZW 6 (jump not taken), 10 (jump taken)

JBC 5 (jump not taken), 9 (jump taken)

JBS 5 (jump not taken), 9 (jump taken)

JC 4 (jump not taken), 8 (jump taken)

JE 4 (jump not taken), 8 (jump taken)

JGE 4 (jump not taken), 8 (jump taken)

JGT 4 (jump not taken), 8 (jump taken)

JH 4 (jump not taken), 8 (jump taken)

JLE 4 (jump not taken), 8 (jump taken)

JLT 4 (jump not taken), 8 (jump taken)

JNC 4 (jump not taken), 8 (jump taken)

JNE 4 (jump not taken), 8 (jump taken)

JNH 4 (jump not taken), 8 (jump taken)

JNST 4 (jump not taken), 8 (jump taken)

JNV 4 (jump not taken), 8 (jump taken)

JNVT 4 (jump not taken), 8 (jump taken)

JST 4 (jump not taken), 8 (jump taken)

JV 4 (jump not taken), 8 (jump taken)

JVT 4 (jump not taken), 8 (jump taken)

Shift

Mnemonic Direct

NORML 8 + 1 per shift (9 for 0 shift)

SHL 6 + 1 per shift (7 for 0 shift)

SHLB 6 + 1 per shift (7 for 0 shift)

SHLL 7 + 1 per shift (8 for 0 shift)

SHR 6 + 1 per shift (7 for 0 shift)

SHRA 6 + 1 per shift (7 for 0 shift)

SHRAB 6 + 1 per shift (7 for 0 shift)

SHRAL 7 + 1 per shift (8 for 0 shift)

SHRB 6 + 1 per shift (7 for 0 shift)

SHRL 7 + 1 per shift (8 for 0 shift)

Table A-9. Instruction Execution Times (in State Times) (Continued)

NOTE: The column entitled “Reg.” lists the instruction execution times for accesses to the register file or

peripheral SFRs. The column entitled “Mem.” lists the instruction execution times for accesses to

all memory-mapped registers, I/O, or memory. See Table 5-1 on page 5-4 for address information.