13-33

INTERFACING WITH EXTERNAL MEMORY

13.7.4 Regaining Bus Control

While HOLD# is asserted, the 8XC196Nx continues executing code until it needs to access the

external bus. If executing from internal memory, it continues until it needs to perform an external

memory cycle. If executing from external memory, it continues executing until the queue is emp-

ty or until it needs to perform an external data cycle. As soon as it needs to access the external

bus, the 8XC196Nx asserts BREQ# and waits for the external device to deassert HOLD#. After

asserting BREQ#, the 8XC196Nx cannot respond to any interrupt requests, including NMI, until

the external device deasserts HOLD#. One state time after HOLD# goes high, the 8XC196Nx

deasserts HLDA# and, with no delay, resumes control of the bus.

If the 8XC196Nx is reset while in hold, bus contention can occur. For example, a CPU-only de-

vice would try to fetch the chip configuration byte from external memory after RESET# was

brought high. Bus contention would occur because both the external device and the 8XC196Nx

would attempt to access memory. One solution is to use the RESET# signal as the system reset;

then all bus masters (including the 8XC196Nx) are reset at once. Chapter 11, “Minimum Hard-

ware Considerations,” shows system reset circuit examples.

13.8 WRITE-CONTROL MODES

The device has two write-control modes: the standard mode, which uses the WR# and BHE# sig-

nals, and the write strobe mode, which uses the WRL# and WRH# signals. Otherwise, the two

modes are identical. The modes are selected by chip configuration register 0 (Figure 13-6 on page

13-15.)

Figure 13-17 shows the waveforms of the asserted write-control signals in the two modes. Note

that only BHE# is valid throughout the bus cycle.

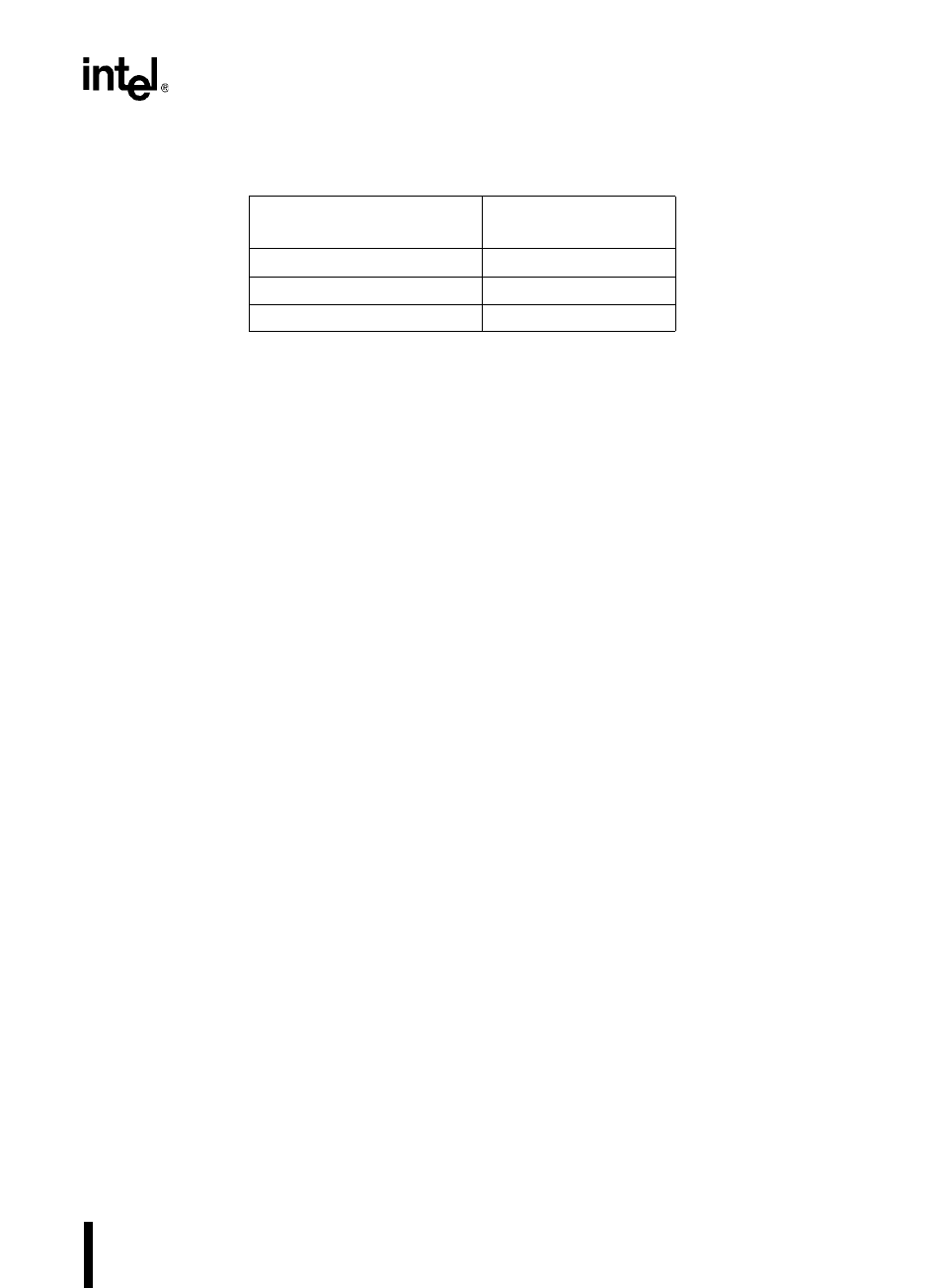

Table 13-13. Maximum Hold Latency

Bus Cycle Type

Maximum Hold Latency

(state times)

Internal execution or idle mode 1.5

16-bit external execution 2.5 + 1 per wait state

8-bit external execution 2.5 + 2 per wait state