8XC196NP, 80C196NU USER’S MANUAL

6-12

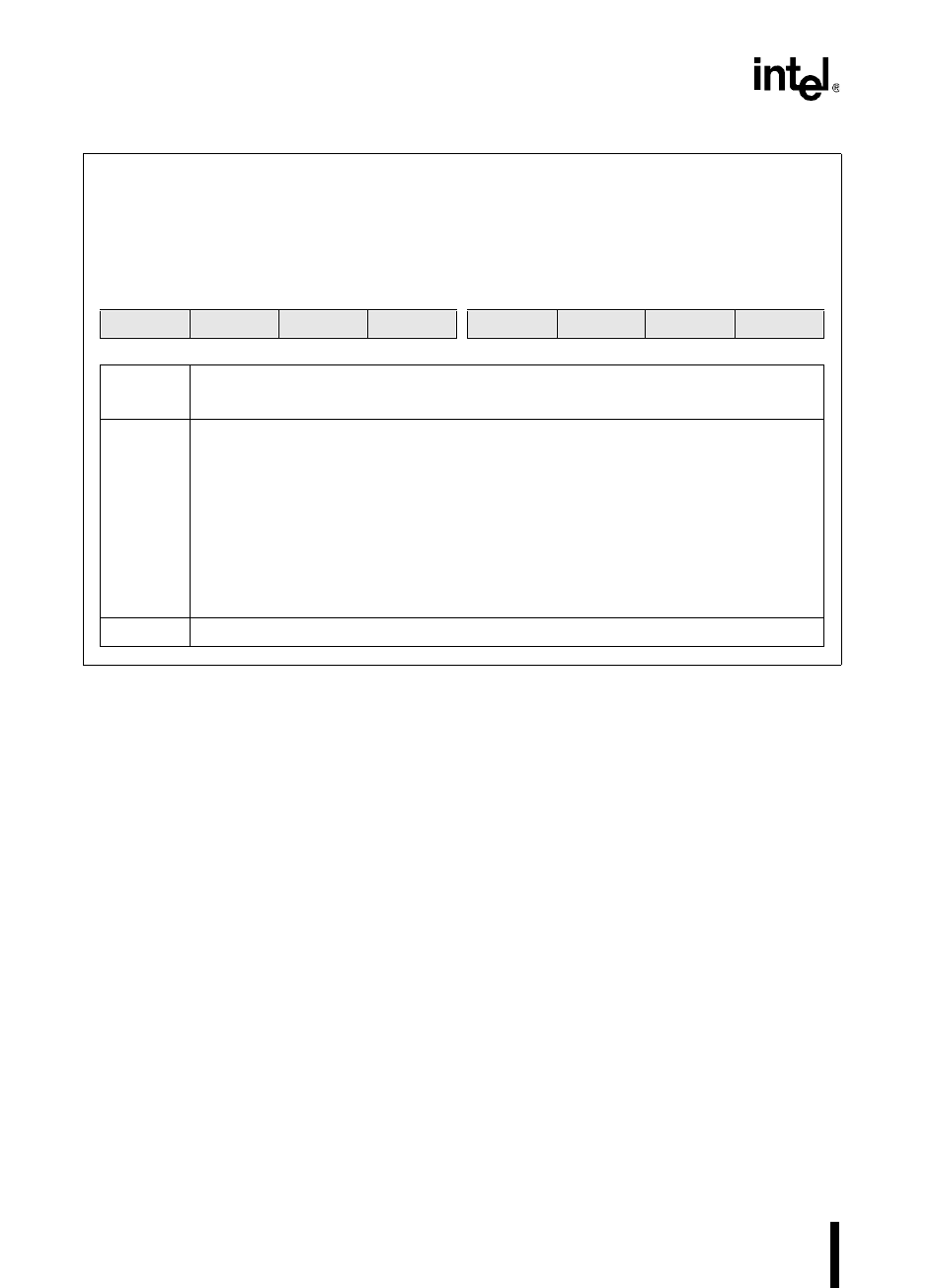

INT_MASK

Address:

Reset State:

0008H

00H

The interrupt mask (INT_MASK) register enables or disables (masks) individual interrupt requests.

(The EI and DI instructions enable and disable servicing of all maskable interrupts.) INT_MASK is the

low byte of the processor status word (PSW); therefore, PUSHF or PUSHA saves this register on the

stack and POPF or POPA restores it.

7 0

EPA0 RI TI EXTINT1 EXTINT0 — OVRTM2 OVRTM1

Bit

Number

Function

7:3

1:0

Setting a bit enables the corresponding interrupt.

The standard interrupt vector locations are as follows:

Bit Mnemonic Interrupt Standard Vector

EPA0 EPA Capture/Compare Channel 0 FF200EH

RI SIO Receive FF200CH

TI SIO Transmit FF200AH

EXTINT1 EXTINT1 pin FF2008H

EXTINT0 EXTINT0 pin FF2006H

OVRTM2 Timer 2 Overflow/Underflow FF2002H

OVRTM1 Timer 1 Overflow/Underflow FF2000H

2 Reserved; for compatibility with future devices, write zero to this bit.

Figure 6-5. Interrupt Mask (INT_MASK) Register