A-45

INSTRUCTION SET REFERENCE

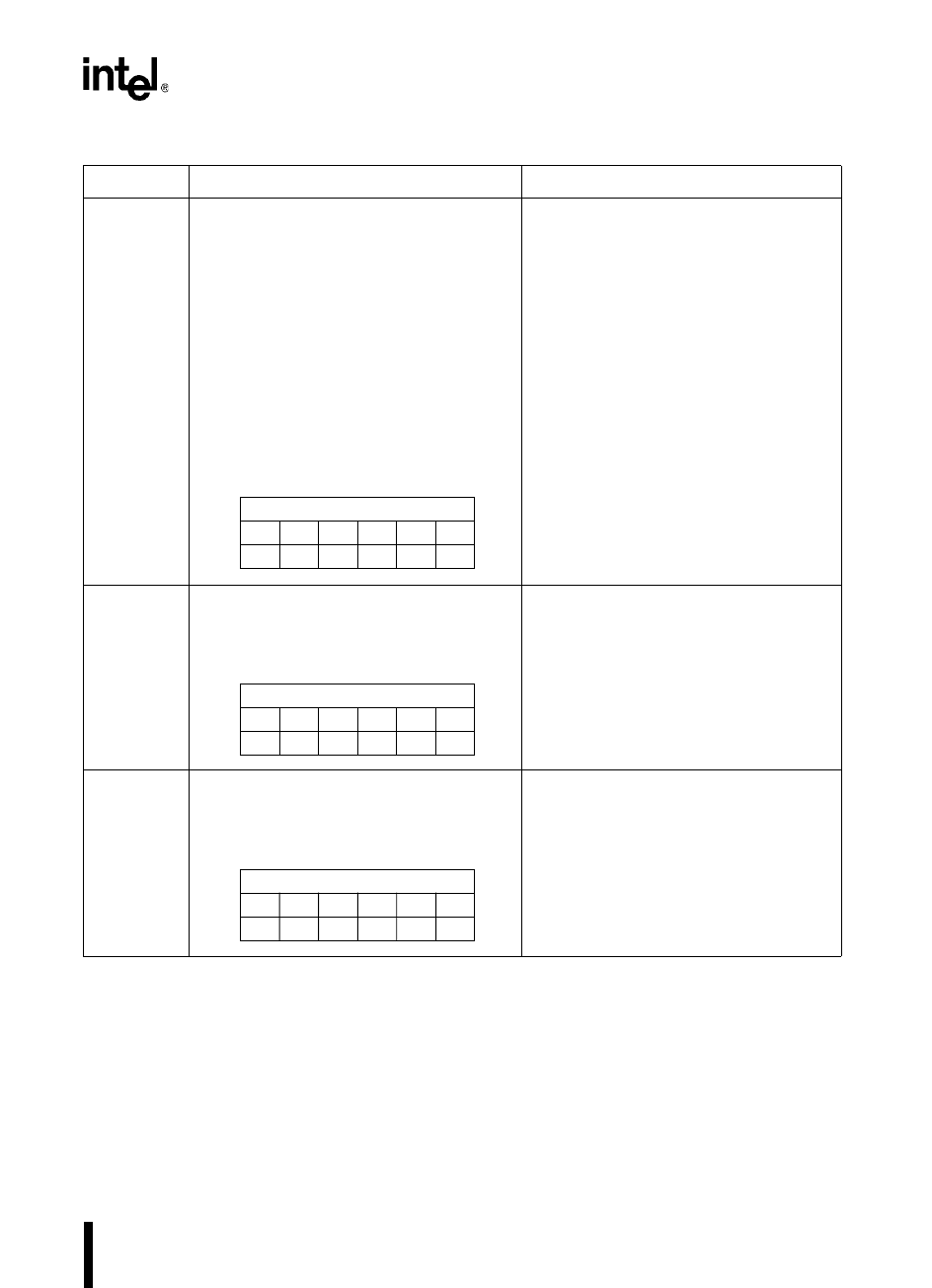

TRAP SOFTWARE TRAP. This instruction causes

an interrupt call that is vectored through

location FF2010H. The operation of this

instruction is not affected by the state of the

interrupt enable flag (I) in the PSW. Interrupt

calls cannot occur immediately following this

instruction.

64-Kbyte mode:

SP

← SP – 2

(SP)

← PC

PC

← (2010H)

1-Mbyte mode:

SP

← SP – 4

(SP)

← PC

PC

← (0FF2010H)

TRAP

(11110111)

NOTE: This instruction is not supported

by assemblers. The TRAP

instruction is intended for use by

development tools. These tools

may not support user-application

of this instruction.

PSW Flag Settings

ZNCVVTST

——————

XCH EXCHANGE WORD. Exchanges the value of

the source word operand with that of the

destination word operand.

(DEST)

↔ (SRC)

DEST, SRC

XCH wreg, waop

(00000100) (waop) (wreg) direct

(00001011) (waop) (wreg) indexed

PSW Flag Settings

ZNCVVTST

——————

XCHB EXCHANGE BYTE. Exchanges the value of

the source byte operand with that of the

destination byte operand.

(DEST)

↔ (SRC)

DEST, SRC

XCHB breg, baop

(00010100) (baop) (breg) direct

(00011011) (baop) (breg) indexed

PSW Flag Settings

ZNCVVTST

——————

Table A-6. Instruction Set (Continued)

Mnemonic Operation Instruction Format