8XC196NP, 80C196NU USER’S MANUAL

A-18

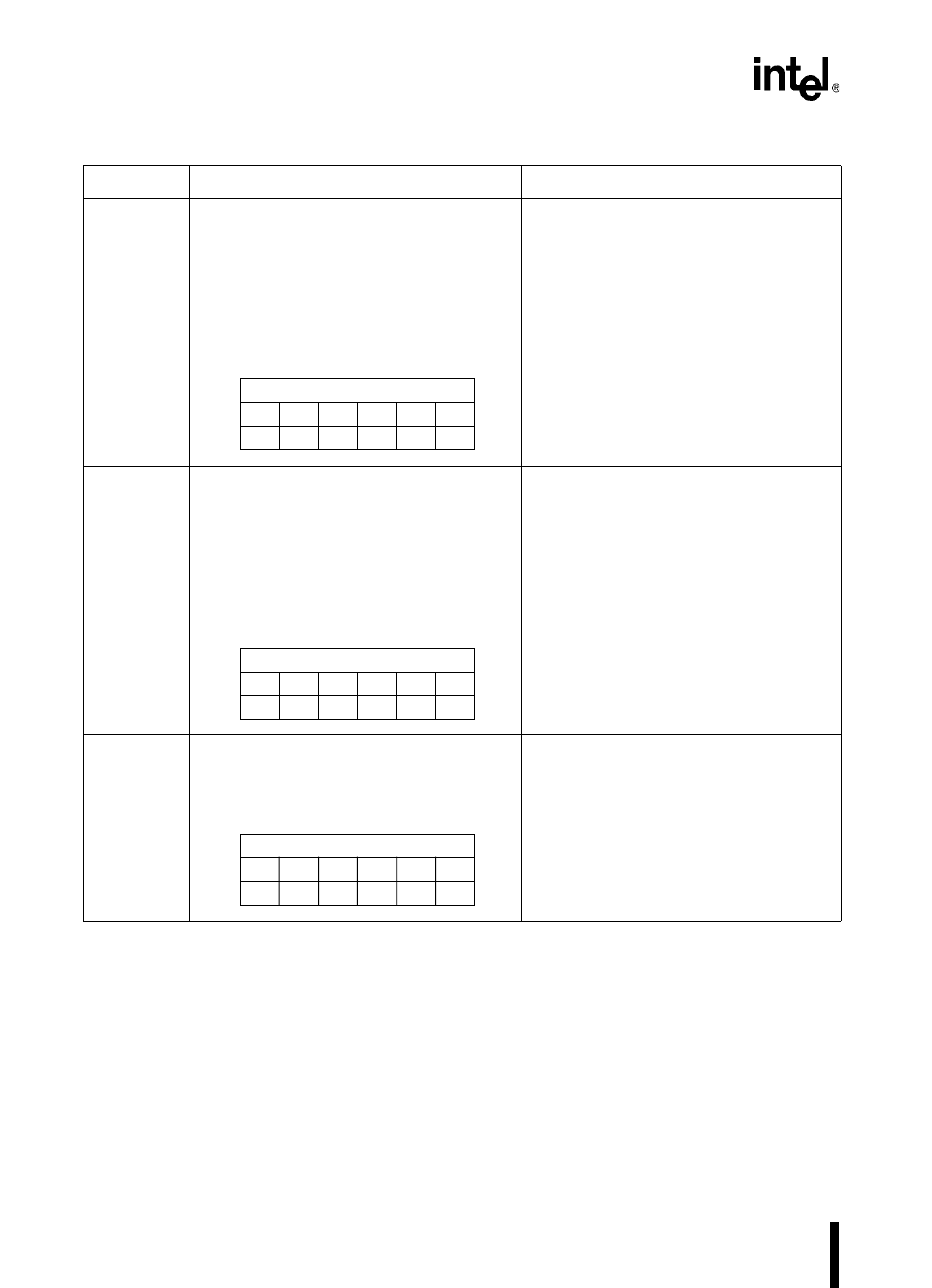

ELD EXTENDED LOAD WORD. Loads the value

of the source word operand into the

destination operand.

This instruction allows you to move data from

anywhere in the 16-Mbyte address space into

the lower register file.

ext. indirect: (DEST)

← (SRC)

ext indexed: (DEST)

← (SRC) + 24-bit disp

DEST, SRC

ELD wreg, [treg]

ext. indirect: (11101000) (treg) (wreg)

ext. indexed: (11101001) (treg) (disp-low)

(disp-high) (disp-ext) (wreg)

NOTE: For 20-bit addresses, the offset

must be in the range of +524287

to –524288.

PSW Flag Settings

ZNCVVTST

——————

ELDB EXTENDED LOAD BYTE. Loads the value of

the source byte operand into the destination

operand.

This instruction allows you to move data from

anywhere in the 16-Mbyte address space into

the lower register file.

ext. indirect: (DEST)

← (SRC)

ext indexed: (DEST)

← (SRC) + 24-bit disp

DEST, SRC

ELDB breg, [treg]

ext. indirect: (11101010) (treg) (breg)

ext. indexed: (11101011) (treg) (disp-low)

(disp-high) (disp-ext) (breg)

NOTE: For 20-bit addresses, the offset

must be in the range of +524287

to –524288.

PSW Flag Settings

ZNCVVTST

——————

EPTS ENABLE PERIPHERAL TRANSACTION

SERVER (PTS). Enables the peripheral

transaction server (PTS).

PTS Enable (PSW.2)

← 1

EPTS

(11101101)

PSW Flag Settings

ZNCVVTST

——————

Table A-6. Instruction Set (Continued)

Mnemonic Operation Instruction Format