9-3

PULSE-WIDTH MODULATOR

9.3 PWM OPERATION

For the 8XC196NP, CON_REG0.0 (CLK0) controls the PWM output frequency by enabling or

disabling the divide-by-two clock prescaler. Enabling the prescaler causes the 8-bit counter to in-

crement once every two state times; disabling it causes the counter to increment once every state

time.

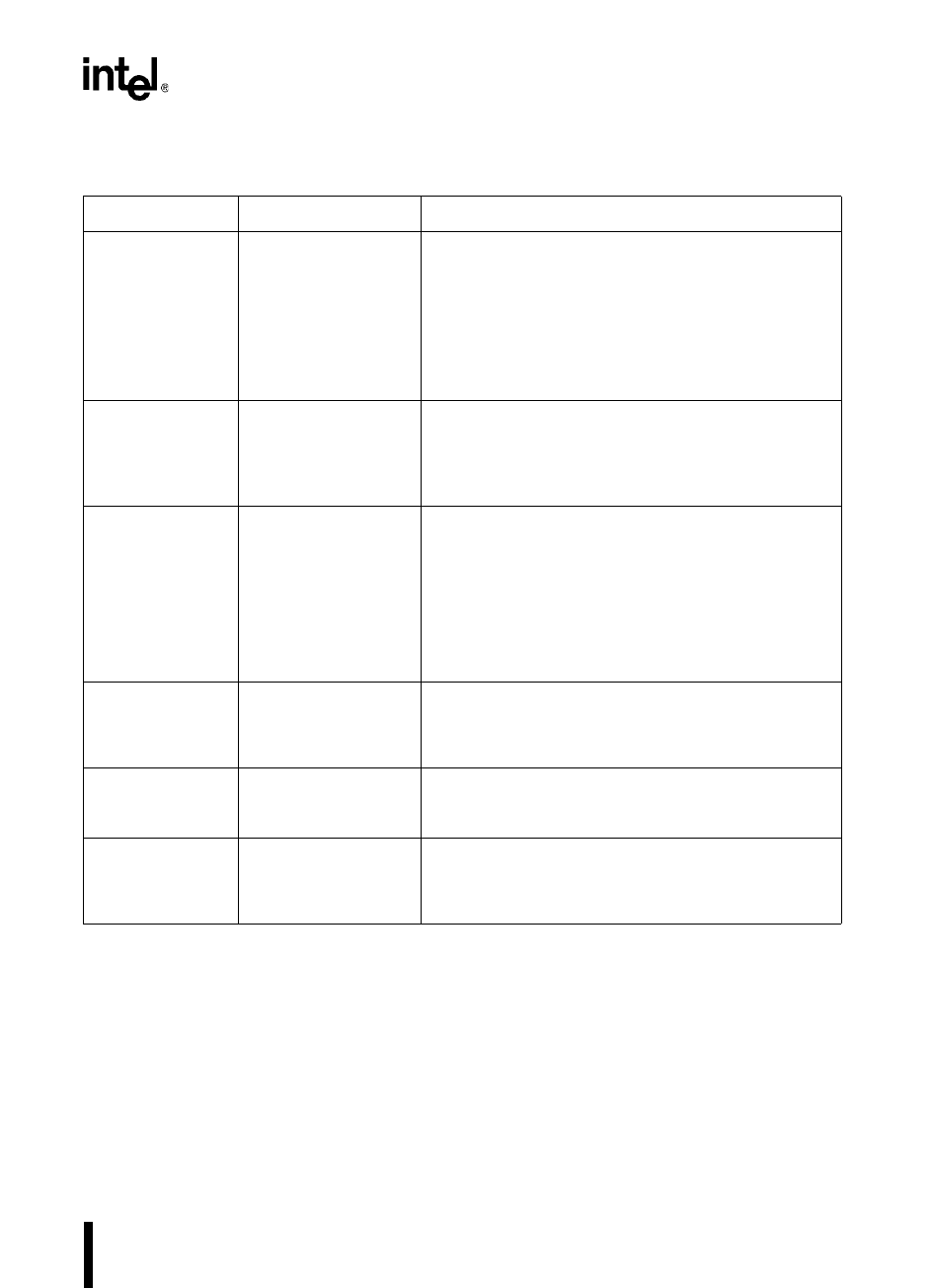

Table 9-2. PWM Control and Status Registers

Mnemonic Address Description

CON_REG0 1FB6H PWM Control Register

This register controls the clock prescaler.

Bit 0 (CLK0) controls the output period of the PWM

channels by enabling or disabling the divide-by-two clock

prescaler (8XC196NP only).

Bits 0 and 1 (CLK0, CLK1) control the output period of the

PWM channels by enabling or disabling the divide-by-two

or divide-by-four clock prescaler (80C196NU only).

PWM0_CONTROL

PWM1_CONTROL

PWM2_CONTROL

1FB0H

1FB2H

1FB4H

PWM Duty Cycle

This register controls the PWM duty cycle. A zero loaded

into this register causes the PWM to output a low continu-

ously (0% duty cycle). An FFH in this register causes the

PWM to have its maximum duty cycle (99.6% duty cycle).

P4_DIR 1FDBH Port 4 Direction

The P4_DIR register determines the I/O mode for each

port 4 pin. The register settings for an open-drain output or

a high-impedance input are identical. An open-drain

output configuration requires an external pull-up. A high-

impedance input configuration requires that the corre-

sponding bit in P4_REG be set. This port has a higher

drive capability than the other ports in order to support

PWM high-drive output requirements.

P4_MODE 1FD9H Port 4 Mode

Each bit in this register determines whether the corre-

sponding pin functions as a standard I/O port pin or is

used for a special-function signal.

P4_PIN 1FDFH Port 4 Pin State

P4_PIN contains the current state of each port pin,

regardless of the pin mode setting.

P4_REG 1FDDH Port 4 Output Data

P4_REG contains data to be driven out by the respective

pins. When a port pin is configured as an input, the corre-

sponding bit in P4_REG must be set.