A-9

INSTRUCTION SET REFERENCE

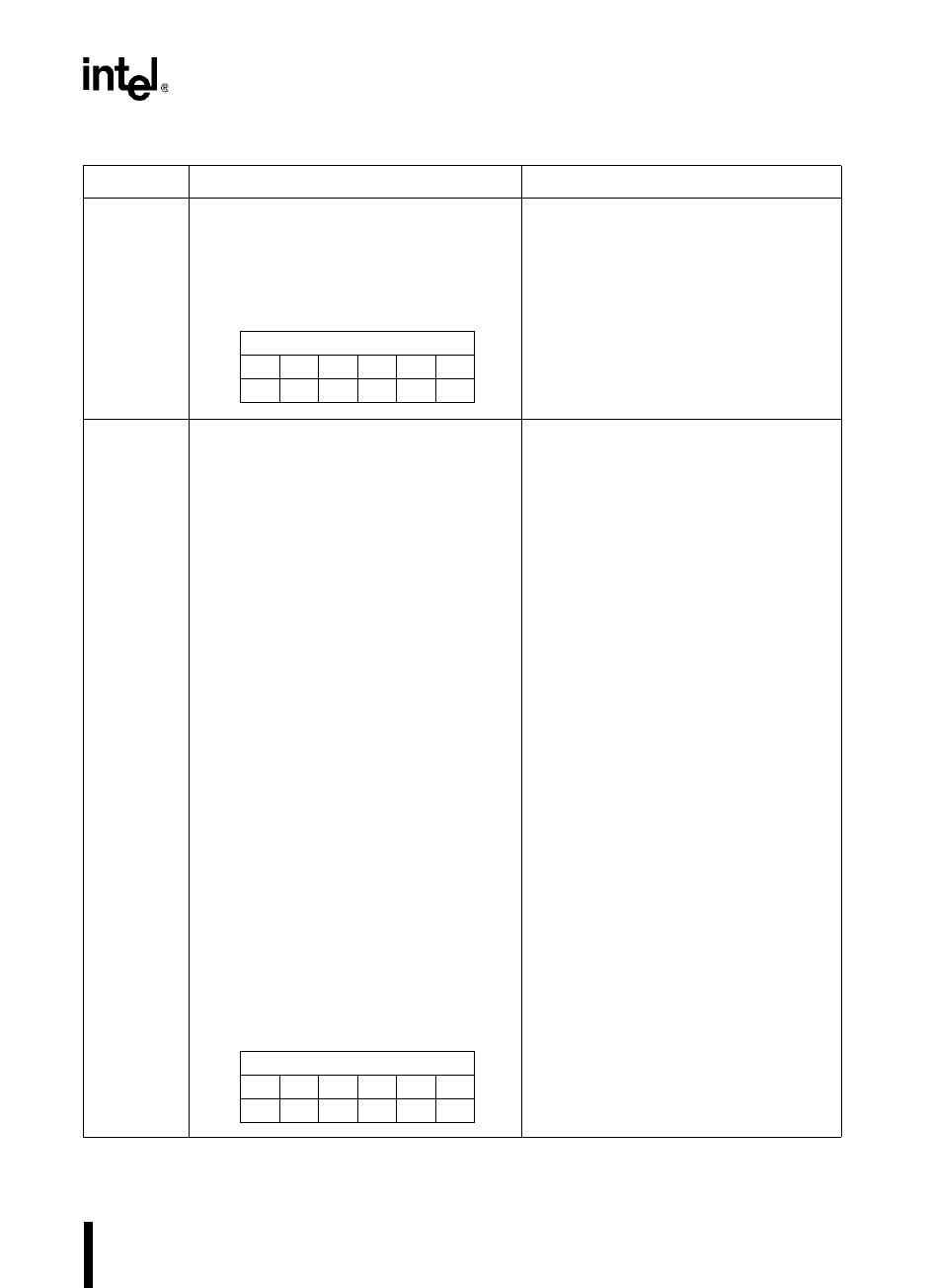

ANDB

(3 operands)

LOGICAL AND BYTES. ANDs the two source

byte operands and stores the result into the

destination operand. The result has ones in

only the bit positions in which both operands

had a “1” and zeros in all other bit positions.

(DEST)

← (SRC1) AND (SRC2)

DEST, SRC1, SRC2

ANDB Dbreg, Sbreg, baop

(010100aa) (baop) (Sbreg) (Dbreg)

PSW Flag Settings

ZNCVVTST

✓✓00——

BMOV BLOCK MOVE. Moves a block of word data

from one location in memory to another. The

source and destination addresses are

calculated using the indirect with autoin-

crement addressing mode. A long register

(PTRS) addresses the source and destination

pointers, which are stored in adjacent word

registers. The source pointer (SRCPTR) is

the low word and the destination pointer

(DSTPTR) is the high word of PTRS. A word

register (CNTREG) specifies the number of

transfers. The blocks of data can be located

anywhere in page 00H of register RAM, but

should not overlap. Because the source

(SRCPTR) and destination (DSTPTR)

pointers are 16 bits wide, this instruction uses

nonextended data moves. It cannot operate

across page boundaries. For example,

SRCPTR cannot point to a location on page

05 while DSTPTR points to page 00.

SRCPTR and DSTPTR will operate from the

page defined by EP_REG. EP_REG should

be set to 00H to select page 00H (see

“Accessing Data” on page 5-23). (The

80C196NU forces EP_REG to 00H.)

COUNT

← (CNTREG)

LOOP: SRCPTR

← (PTRS)

DSTPTR

← (PTRS + 2)

(DSTPTR)

← (SRCPTR)

(PTRS)

← SRCPTR + 2

(PTRS + 2)

← DSTPTR + 2

COUNT

← COUNT – 1

if COUNT

≠ 0 then

go to LOOP

PTRS, CNTREG

BMOV lreg, wreg

(11000001) (wreg) (lreg)

NOTE: The pointers are autoincre-

mented during this instruction.

However, CNTREG is not decre-

mented. Therefore, it is easy to

unintentionally create a long,

uninterruptible operation with the

BMOV instruction. Use the

BMOVI instruction for an interrupt-

ible operation.

PSW Flag Settings

ZNCVVTST

——————

Table A-6. Instruction Set (Continued)

Mnemonic Operation Instruction Format