6-25

STANDARD AND PTS INTERRUPTS

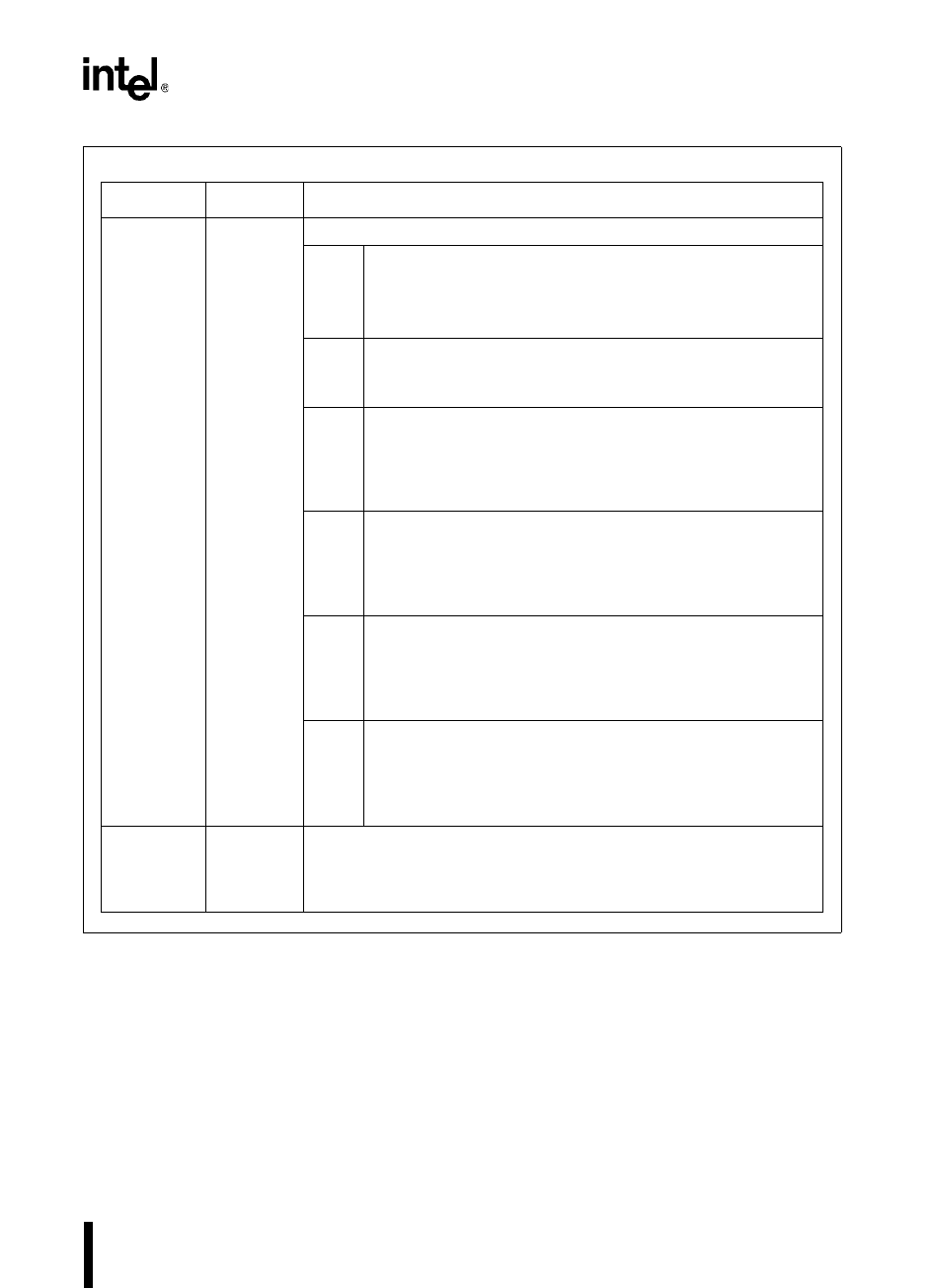

Register Location Function

PTSCON PTSCB + 1 PTS Control Bits

M2:0 PTS Mode

These bits select the PTS mode:

M2 M1 M0

000block transfer mode

BW Byte/Word Transfer

0 = word transfer

1 = byte transfer

SU Update PTSSRC

0 = reload original PTS source address after each block

transfer is complete

1 = retain current PTS source address after each block transfer

is complete

DU Update PTSDST

0 = reload original PTS destination address after each block

transfer is complete

1 = retain current PTS destination address after each block

transfer is complete

SI PTSSRC Autoincrement

0 = do not increment the contents of PTSSRC after each byte

or word transfer

1 = increment the contents of PTSSRC after each byte or word

transfer

DI PTSDST Autoincrement

0 = do not increment the contents of PTSDST after each byte

or word transfer

1 = increment the contents of PTSDST after each byte or word

transfer

PTSCOUNT PTSCB + 0 Consecutive Block Transfers

Defines the number of blocks that will be transferred during the block

transfer routine. Each block transfer is one PTS cycle. Maximum number

is 255.

PTS Block Transfer Mode Control Block (Continued)

Figure 6-13. PTS Control Block — Block Transfer Mode (Continued)