9-9

PULSE-WIDTH MODULATOR

9.5.1 Sample Calculations

For example, assume that the operating frequency equals 25 MHz, the desired period of the PWM

output waveform is either 20.48 µs (512 state times) if the divide-by-two prescaler is disabled or

40.96 µs (1,024 state times) if the prescaler is enabled. If PWMx_CONTROL equals 8AH (138

decimal), the pulsewidth is held high for 11.04 µs (and low for 9.44 µs) of the total 20.48 µs pe-

riod, resulting in a duty cycle of approximately 54%. If the prescaler is enabled, the same values

would produce a period of 40.96 µs with the pulsewidth being held high for 22.08 µs (and low for

18.88 µs), for the same duty cycle, approximately 54%.

9.5.2 Enabling the PWM Outputs

Each PWM output is multiplexed with a port pin, so you must configure it as a special-function

output signal before using the PWM function. To do so, follow this sequence:

1. Clear the corresponding bit of P4_DIR (see Table 9-5).

2. Set the corresponding bit of P4_MODE (see Table 9-5).

3. Set or clear the corresponding bit of P4_REG (see Table 9-5).

Table 9-5 shows the alternate port function along with the register setting that selects the PWM

output instead of the port function.

9.5.3 Generating Analog Outputs

The PWM modules can generate a rectangular pulse train that varies in duty cycle and period.

Filtering this output will create a smooth analog signal. To make a signal swing over the desired

analog range, first buffer the signal and then filter it with either a simple RC network or an active

filter. Figure 9-6 is a block diagram of the type of circuit needed to create the smooth analog sig-

nal.

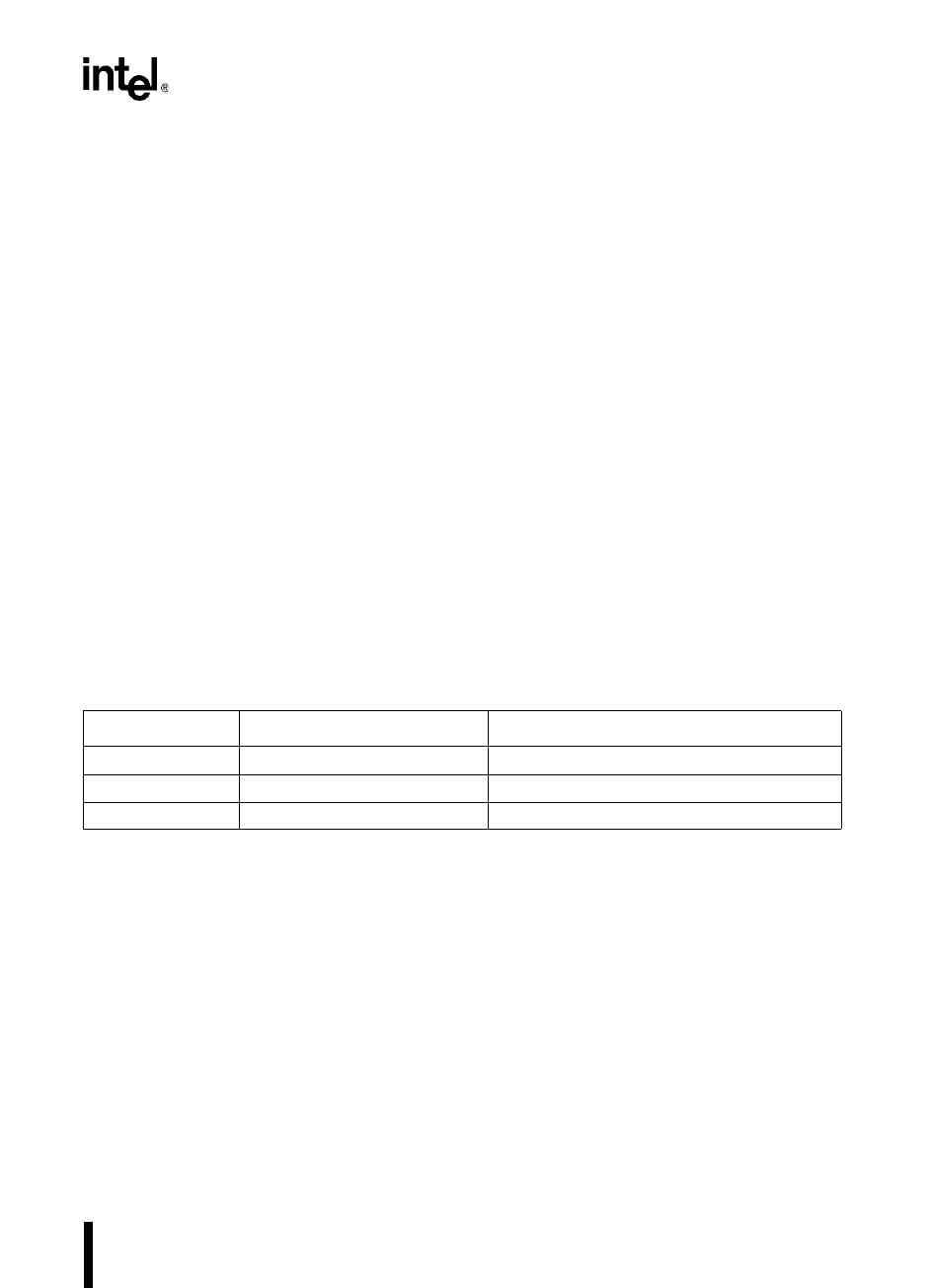

Table 9-5. PWM Output Alternate Functions

PWM Output Alternate Port Function PWM Output Enabled When:

PWM0 P4.0 P4_DIR.0 = 0, P4_MODE.0 = 1, P4_REG = X

PWM1 P4.1 P4_DIR.1 = 0, P4_MODE.1 = 1, P4_REG = X

PWM2 P4.2 P4_DIR.2 = 0, P4_MODE.2 = 1, P4_REG = X