13-31

INTERFACING WITH EXTERNAL MEMORY

.

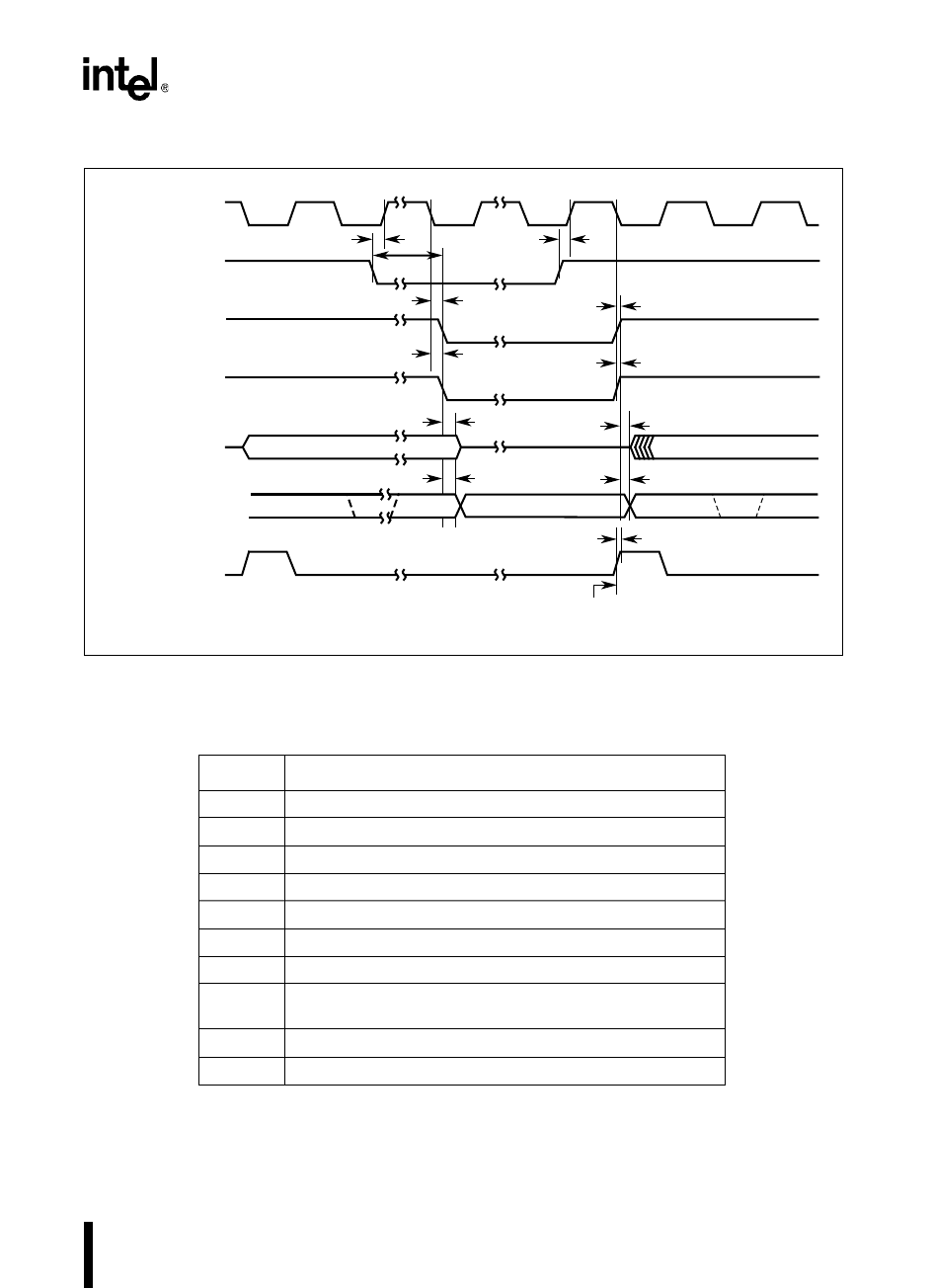

Figure 13-16. HOLD#, HLDA# Timing

When the external device is finished with the bus, it relinquishes control by driving HOLD# high.

In response, the 8XC196Nx deasserts HLDA# and resumes control of the bus.

Table 13-12. HOLD#, HLDA# Timing Definitions

Symbol Parameter

T

HVCH

HOLD# Setup Time

T

CLHAL

CLKOUT Low to HLDA# Low

T

CLHAH

CLKOUT Low to HLDA# High

T

CLBRL

CLKOUT Low to BREQ# Low

T

CLBRH

CLKOUT Low to BREQ# High

T

HALAZ

HLDA# Low to Address Float

T

HAHAX

HLDA# High to Address No Longer Float

T

HALBZ

HLDA# Low to BHE#, INST, RD#, WR#, WRL#, WRH#

Weakly Driven

T

HAHBV

HLDA# High to BHE#, INST, RD#, WR#, WRL#, WRH# valid

T

CLLH

Clock Falling to ALE Rising; Use to derive other timings.

A2460-03

CLKOUT

HOLD#

HLDA#

BREQ#

A19:0, AD15:0

CS

x

#, BHE#,

INST, RD#, WR#

WRL#, WRH#

ALE

T

CLLH

T

CLHAH

T

CLBRH

T

HAHAX

T

HAHBV

T

HALBZ

T

HALAZ

T

CLBRL

T

CLHAL

T

HVCH

T

HVCH

Hold Latency

Start of strongly driven ALE

Weakly held inactive