10-9

EVENT PROCESSOR ARRAY (EPA)

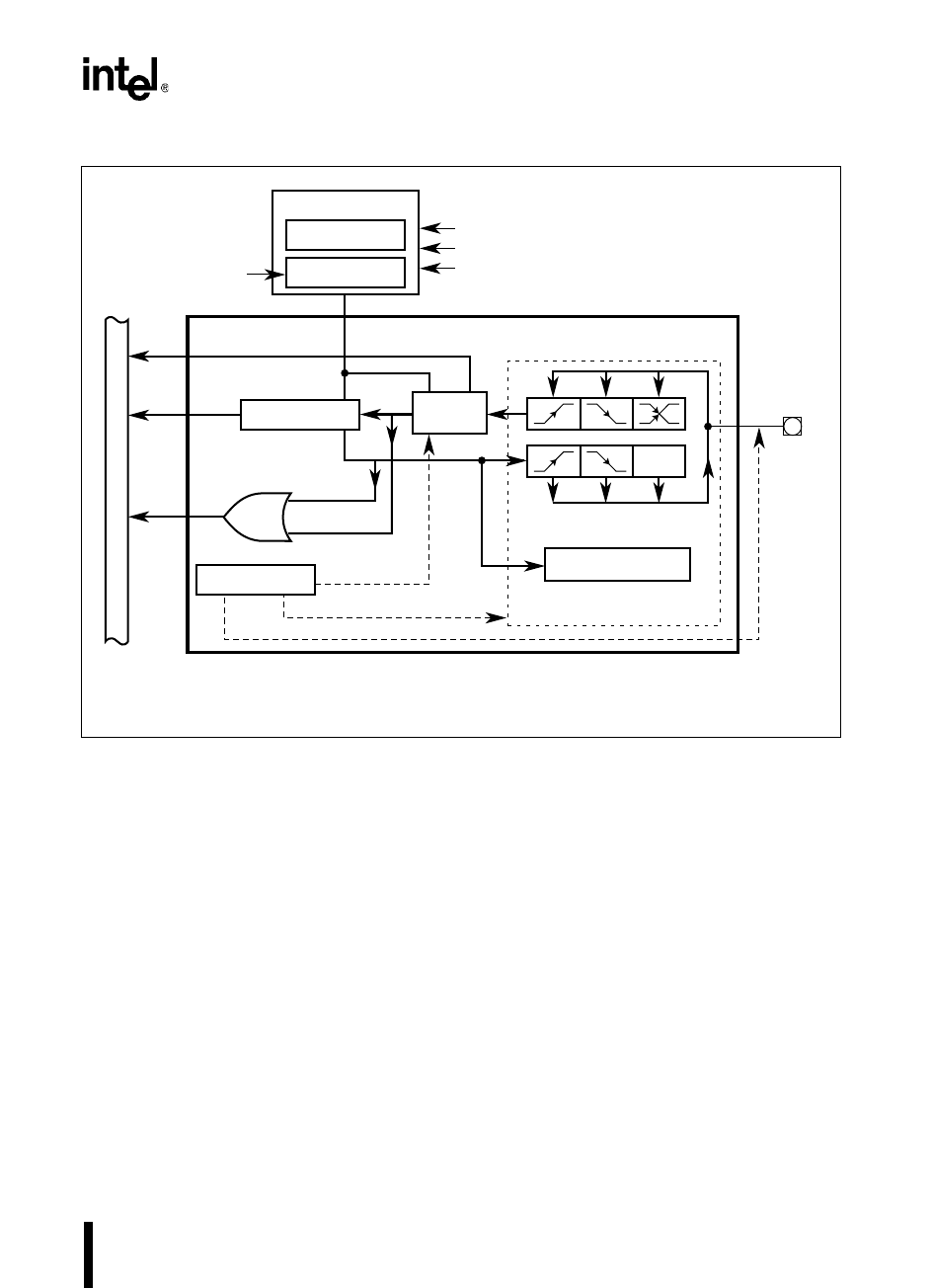

Figure 10-5. A Single EPA Capture/Compare Channel

10.4.1 Operating in Capture Mode

In capture mode, when a valid event occurs on the pin, the value of the selected timer is captured

into a buffer. The timer value is then transferred from the buffer to the EPAx_TIME register,

which sets the EPA interrupt pending bit as shown in Figure 10-6. If enabled, an interrupt is gen-

erated. If a second event occurs before the CPU reads the first timer value in EPAx_TIME, the

current timer value is loaded into the buffer and held there. After the CPU reads the EPAx_TIME

register, the contents of the capture buffer are automatically transferred into EPAx_TIME and the

EPA interrupt pending bit is set.

External clocking (T

x

CLK) with up to 6-bit prescaler

Quadrature clocking through T

x

CLK and T

x

DIR

Internal clocking with up to 6-bit prescaler

Clock on

TIMER1 overflow

TIMER1

TIMER2

EPA

Interrupt

EPA

x

_CON

TGL

Reset Timer

Mode Selection

†

Remap

EPA Pin

EPA

x

_TIME

OVR

x

Interrupt

A0270-02

Timer/Counter Unit

Capture

Buffer

Overwrite

Mode Control

Compare

Capture Overrun

EPA Capture/Compare

Channel

x

†

EPA1 and 3 only. If enabled for EPA1, EPA0 shares the EPA1 pin. If enabled for EPA3, EPA2

shares the EPA3 pin.

Bus