C-55

REGISTERS

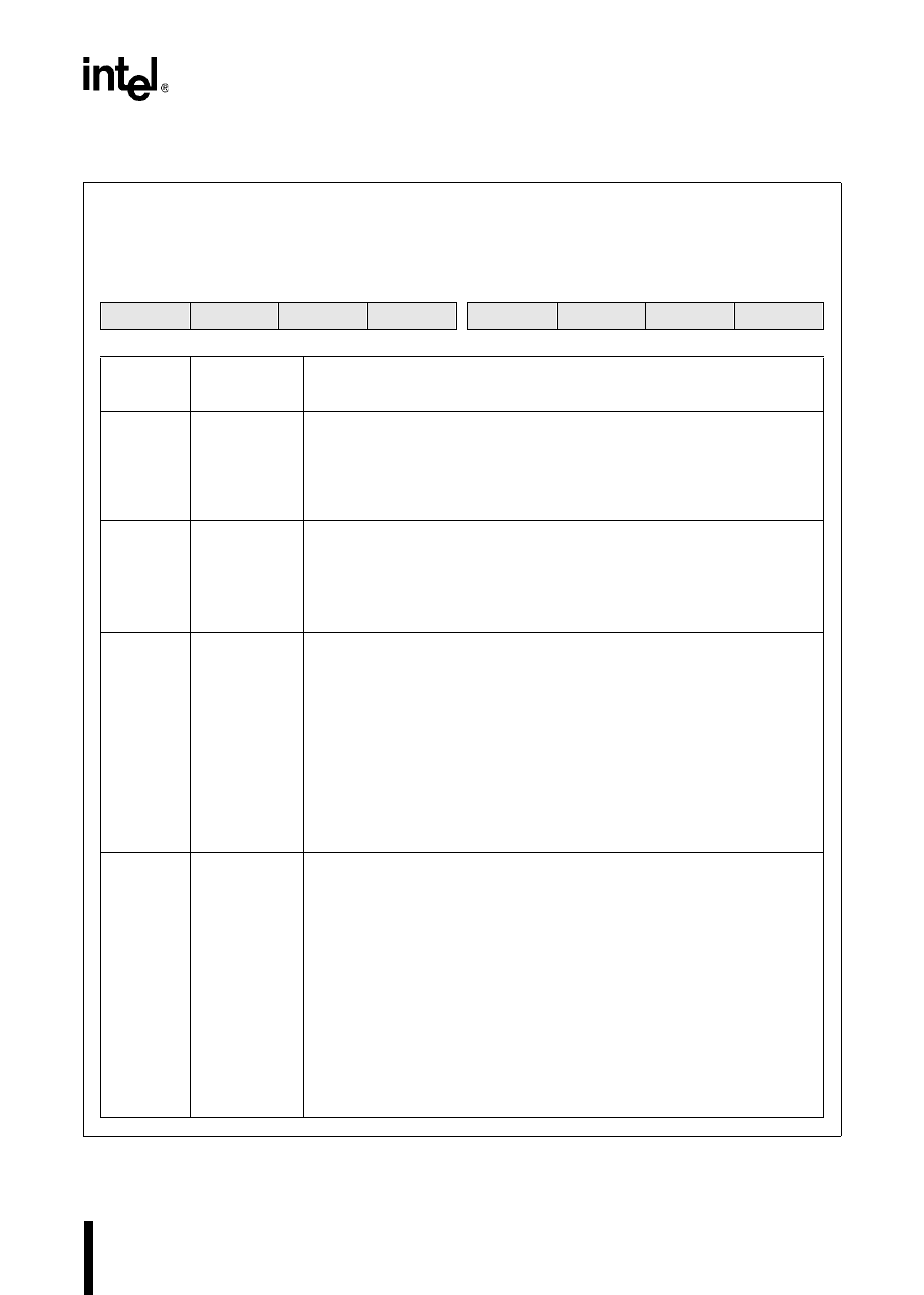

T2CONTROL

T2CONTROL

Address:

Reset State:

1F7CH

00H

The timer 2 control (T2CONTROL) register determines the clock source, counting direction, and count

rate for timer 2.

7 0

CE UD M2 M1 M0 P2 P1 P0

Bit

Number

Bit

Mnemonic

Function

7 CE Counter Enable

This bit enables or disables the timer. From reset, the timers are

disabled and not free running.

0 = disables timer

1 = enables timer

6 UD Up/Down

This bit determines the timer counting direction, in selected modes (see

mode bits, M2:0).

0 = count down

1 = count up

5:3 M2:0 EPA Clock Direction Mode Bits

These bits determine the timer clocking source and direction source.

M2 M1 M0 Clock Source Direction Source

000F

XTAL1

/4 UD bit (T2CONTROL.6)

X 0 1 reserved —

010reserved —

011reserved —

100timer 1 overflow UD bit (T2CONTROL.6)

110timer 1 overflow same as timer 1

1 1 1 reserved —

2:0 P2:0 EPA Clock Prescaler Bits

These bits determine the clock prescaler value.

P2 P1 P0 Prescaler Resolution

†

000divide by 1 (disabled) 250 ns

001divide by 2 500 ns

010divide by 4 1 µs

011divide by 8 2 µs

100divide by 16 4 µs

101divide by 32 8 µs

110divide by 64 16 µs

111reserved —

†

Resolution at 16 MHz. Use the formula on page 11-6 to calculate the

resolution at other frequencies.