5-47

STANDARD AND PTS INTERRUPTS

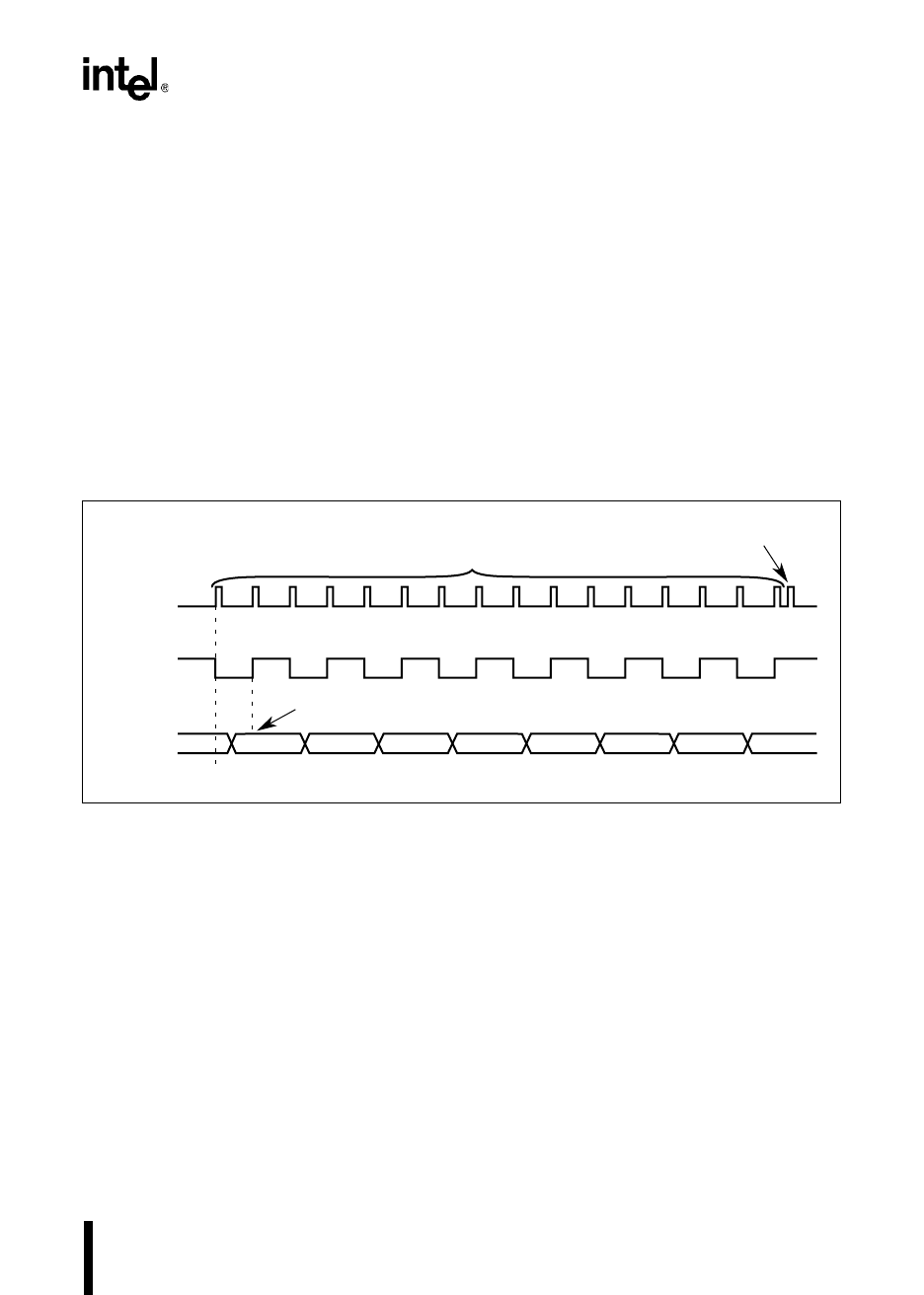

5.6.6.2 Synchronous SIO Receive Mode Example

In synchronous serial I/O (SSIO) receive mode, an EPA channel controls the reception baud rate

by generating or capturing a serial clock signal (SCK). To generate the SCK signal, configure the

EPA channel in compare mode and set the output-pin toggle option. Whenever a match occurs

between the EPA event-time register and a timer register, the EPA channel toggles SCK and gen-

erates an interrupt. If an external source will provide the SCK signal, configure the EPA channel

in capture mode with capture on either edge set. In this case, the EPA channel generates an inter-

rupt whenever the SCK input toggles. On every other EPA interrupt, the PTS inputs a data bit

from a port pin that is configured to function as the Receive Data signal (RXD). PTSCON1 (Fig-

ure 5-19 on page 5-38) controls whether the reception occurs on even or odd PTS cycles. Because

receptions occur only on a rising or falling clock edge, two PTS cycles occur for every one data

bit reception (Figure 5-23). It takes 16 PTS cycles to receive eight data bits. SSIO receptions do

not include parity or stop bits.

Figure 5-23. Synchronous SIO Receive Timing

If the SCK signal is generated by the EPA channel, the first PTS cycle must be started manually.

• Initialize the RXD port pin and the SCK signal to the system-required logic level before

starting a reception.

• Add the contents of the timer register to the Baud_value (Figure 5-19 on page 5-38) and

store the result into the EPA time register. This sets up the timing for the first interrupt and

causes the first interrupt to occur at the proper baud rate.

A3121-01

Interrupts

RXD

(Port pin)

Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6

Bit 7

End-of-PTS

Conventional

Interrupt

16 PTS Serviced Interrupts

SCK

Input Data Sampled on Rising Clock Edge

LSB MSB