7-9

SERIAL I/O (SIO) PORT

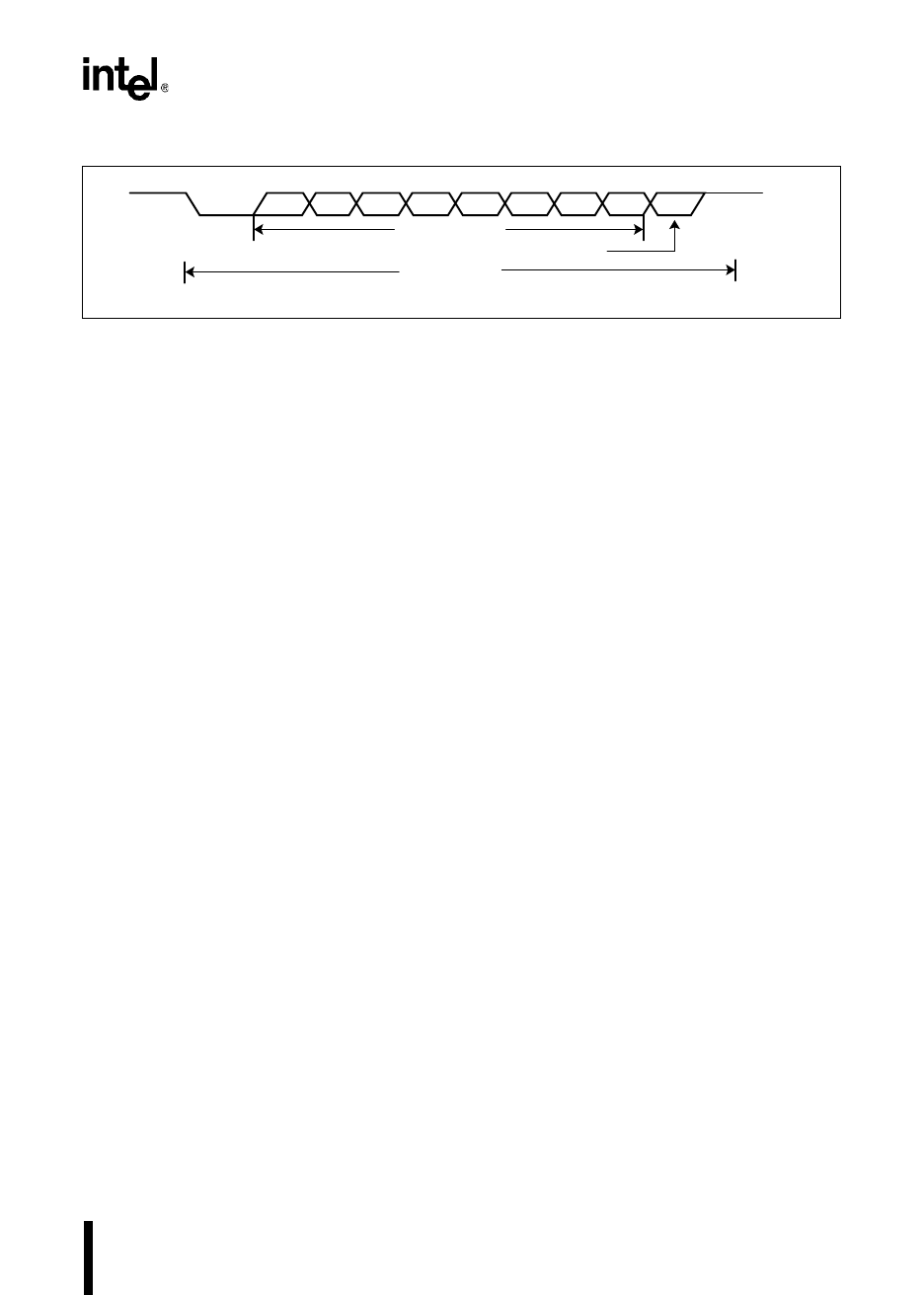

Figure 7-5. Serial Port Frames in Mode 2 and 3

7.3.2.3 Mode 3

Mode 3 is the asynchronous, ninth-bit mode. The data frame for this mode is identical to that of

mode 2. Mode 3 differs from mode 2 during transmissions in that parity can be enabled, in which

case the ninth bit becomes the parity bit. When parity is disabled, data bits 0–7 are written to the

serial port transmit buffer, and the ninth data bit is written to SPx_CON.4 (TB8). In mode 3, a

reception always sets the RIx interrupt pending bit, regardless of the state of the ninth bit. If parity

is disabled, the SPx_STATUS register bit 7 (RB8) contains the ninth data bit. If parity is enabled,

then bit 7 (RB8) is the received parity error (RPE) flag.

7.3.2.4 Mode 2 and 3 Timings

Operation in modes 2 and 3 is similar to mode 1 operation. The only difference is that the data

consists of 9 bits, so 11-bit packages are transmitted and received. During a reception, the RI flag

and the RIx interrupt pending bit are set just after the end of the stop bit. During a transmission,

the TI flag and the TIx interrupt pending bit are set at the beginning of the stop bit. The ninth bit

can be used for parity or multiprocessor communications.

7.3.2.5 Multiprocessor Communications

Modes 2 and 3 are provided for multiprocessor communications. In mode 2, the serial port sets

the RIx interrupt pending bit only when the ninth data bit is set. In mode 3, the serial port sets the

RIx interrupt pending bit regardless of the value of the ninth bit. The ninth bit is always set in

address frames and always cleared in data frames.

One way to use these modes for multiprocessor communication is to set the master processor to

mode 3 and the slave processors to mode 2. When the master processor wants to transmit a block

of data to one of several slaves, it sends out an address frame that identifies the target slave. Be-

cause the ninth bit is set, an address frame interrupts all slaves. Each slave examines the address

byte to check whether it is being addressed. The addressed slave switches to mode 3 to receive

the data frames, while the slaves that are not addressed remain in mode 2 and are not interrupted.

Start

Stop D0

D1

D2

D3

D4

D5 D6

D7 D8

Stop

8 Bits of Data

11-bit Frame

Programmable 9th Bit

A0111-01