8XC196MC, MD, MH USER’S MANUAL

C-42

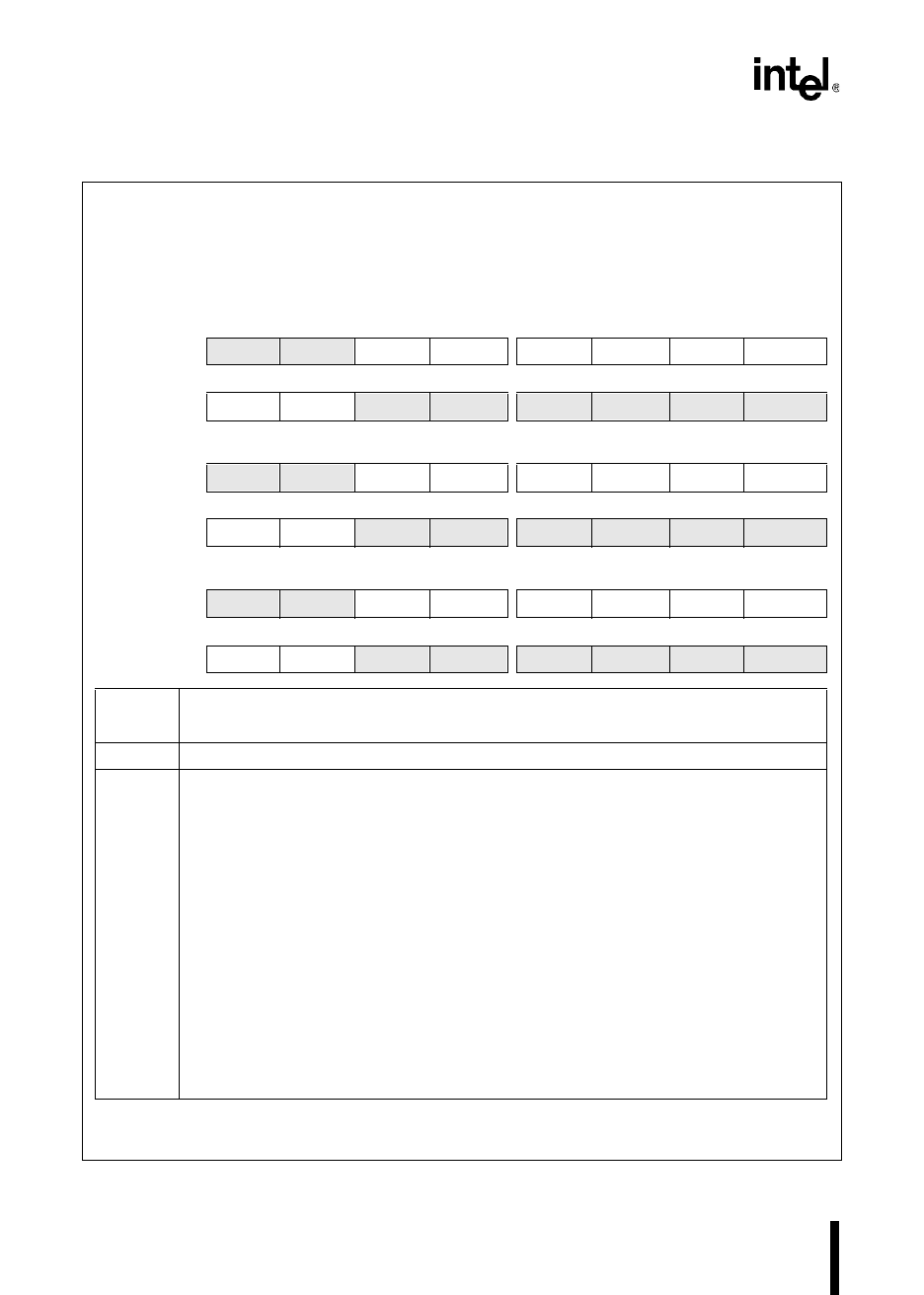

PTSSEL

PTSSEL

Address:

Reset State:

0004H

0000H

The PTS select (PTSSEL) register selects either a PTS microcode routine or a standard interrupt

service routine for each interrupt request. Setting a bit selects a PTS microcode routine; clearing a bit

selects a standard interrupt service routine. When PTSCOUNT reaches zero, hardware clears the

corresponding PTSSEL bit. The PTSSEL bit must be set manually to re-enable the PTS channel.

15 8

8XC196MC

— EXTINT PI — — — COMP3 EPA3

7 0

COMP2 EPA2

COMP1 EPA1 COMP0 EPA0 AD OVRTM

15 8

8XC196MD

— EXTINT PI EPA5 COMP4 EPA4 COMP3 EPA3

7 0

COMP2 EPA2

COMP1 EPA1 COMP0 EPA0 AD OVRTM

15 8

8XC196MH

— EXTINT WG SPI RI1 RI0 TI1 TI0

7 0

COMP3 COMP2

COMP1 EPA1 COMP0 EPA0 AD OVRTM

Bit

Number

Function

15 Reserved; for compatibility with future devices, write zero to this bit.

14:0

†

Setting a bit causes the corresponding interrupt to be handled by a PTS microcode routine.

The PTS interrupt vector locations are as follows:

Bit Mnemonic PTS Vector Bit Mnemonic PTS Vector

EXTINT 205CH TI0 (MH) 2050H

PI (MC, MD)

††

205AH COMP2 (MC,MD) 204EH

WG (MH) 205AH COMP3 (MH) 204EH

EPA5 (MD) 2058H EPA2 (MC, MD) 204CH

SPI (MH)

††

2058H COMP2 (MH) 204CH

COMP4 (MD) 2056H COMP1 204AH

RI1 (MH) 2056H EPA1 2048H

EPA4 (MD) 2054H COMP0 2046H

RI0 (MH) 2054H EPA0 2044H

COMP3 (MC, MD) 2052H AD 2042H

TI1 (MH) 2052H OVRTM

††

2040H

EPA3 (MC, MD) 2050H

††

PTS service is not useful for multiplexed interrupts because the PTS cannot readily

determine the source of these interrupts.

†

On the 8XC196MC device bits 10–12 are reserved. For compatibility with future devices, write zeros

to these bits.