8XC196MC, MD, MH USER’S MANUAL

5-18

5.5.1 Modifying Interrupt Priorities

Your software can modify the default priorities of maskable interrupts by controlling the interrupt

mask registers (INT_MASK and INT_MASK1). For example, you can specify which interrupts,

if any, can interrupt an interrupt service routine. The following code shows one way to prevent

all interrupts, except EXTINT (priority 14), from interrupting an A/D conversion-complete inter-

rupt service routine (priority 01).

SERIAL_RI_ISR:

PUSHA ; Save PSW, INT_MASK, INT_MASK1, & WSR

; (this disables all interrupts)

LDB INT_MASK1, #01000000B ; Enable EXTINT only

EI ; Enable interrupt servicing

; Service the AD_DONE interrupt

POPA ; Restore PSW, INT_MASK, INT_MASK1, &

; WSR registers

RET

CSEG AT 02002H ; fill in interrupt table

DCW AD_DONE_ISR END

0 OVRTM1 Timer 1 Overflow/Underflow

Setting this bit enables the timer 1 overflow/underflow interrupt.

The timer 1 and timer 2 overflow/underflow interrupts are associated with

the overflow/underflow timer interrupt (OVRTM). Setting INT_MASK.0

enables OVRTM.

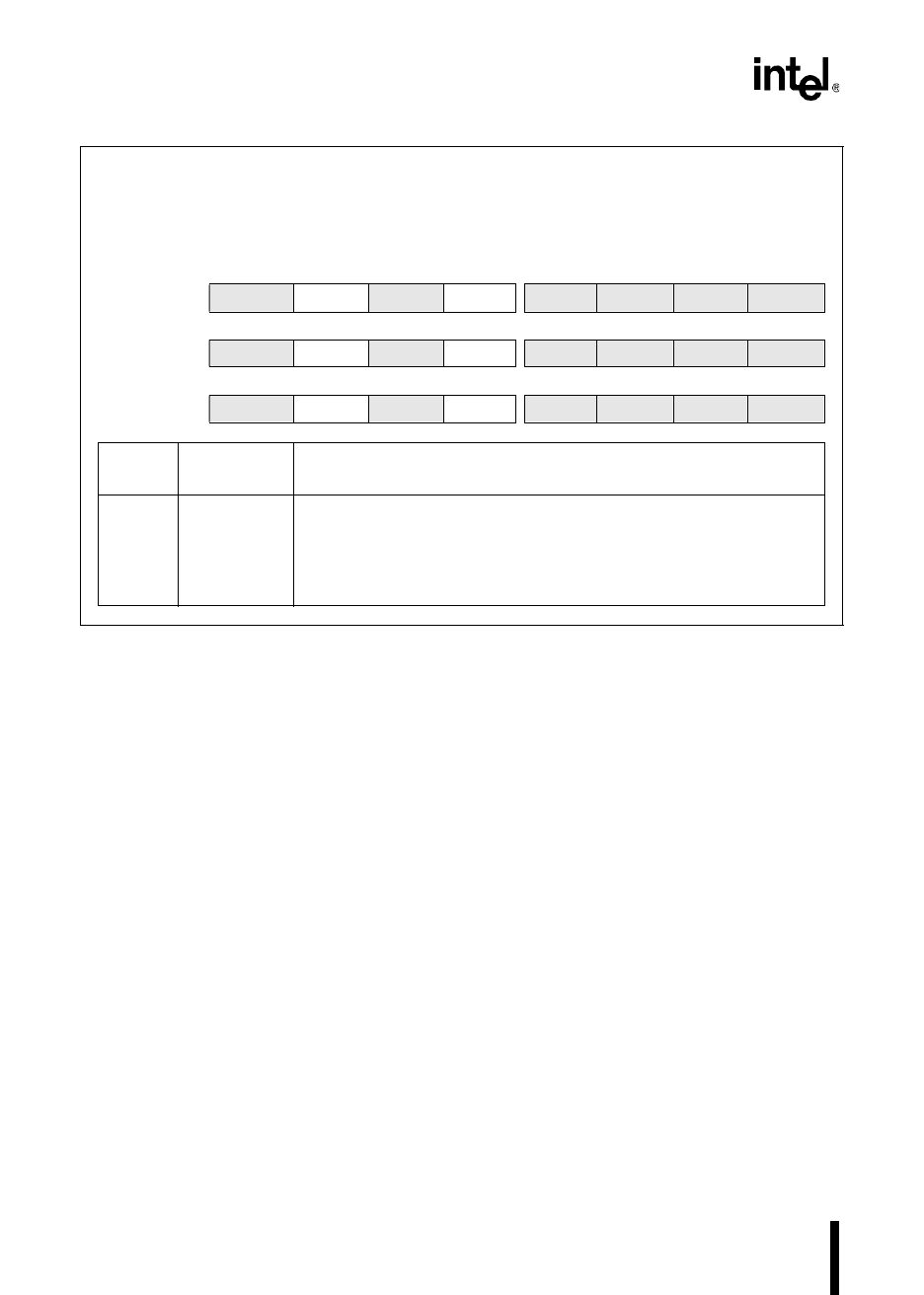

PI_MASK (Continued)

Address:

Reset State:

1FBCH

AAH

The peripheral interrupt mask (PI_MASK) register enables or disables (masks) interrupt requests

associated with the peripheral interrupt (PI), the serial port interrupt (SPI), and the overflow/underflow

timer interrupt (OVRTM).

7 0

8XC196MC

———WG —OVRTM2 — OVRTM1

7 0

8XC196MD

— COMP5 —WG —OVRTM2 — OVRTM1

7 0

8XC196MH

—SP1—SP0 —OVRTM2 — OVRTM1

Bit

Number

Bit

Mnemonic

Function

Figure 5-9. Peripheral Interrupt Mask (PI_MASK) Register (Continued)