© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

User manual Rev. 02 — 23 May 2005 35 of 133

Philips Semiconductors

UM10109

P89LPC932A1 User manual

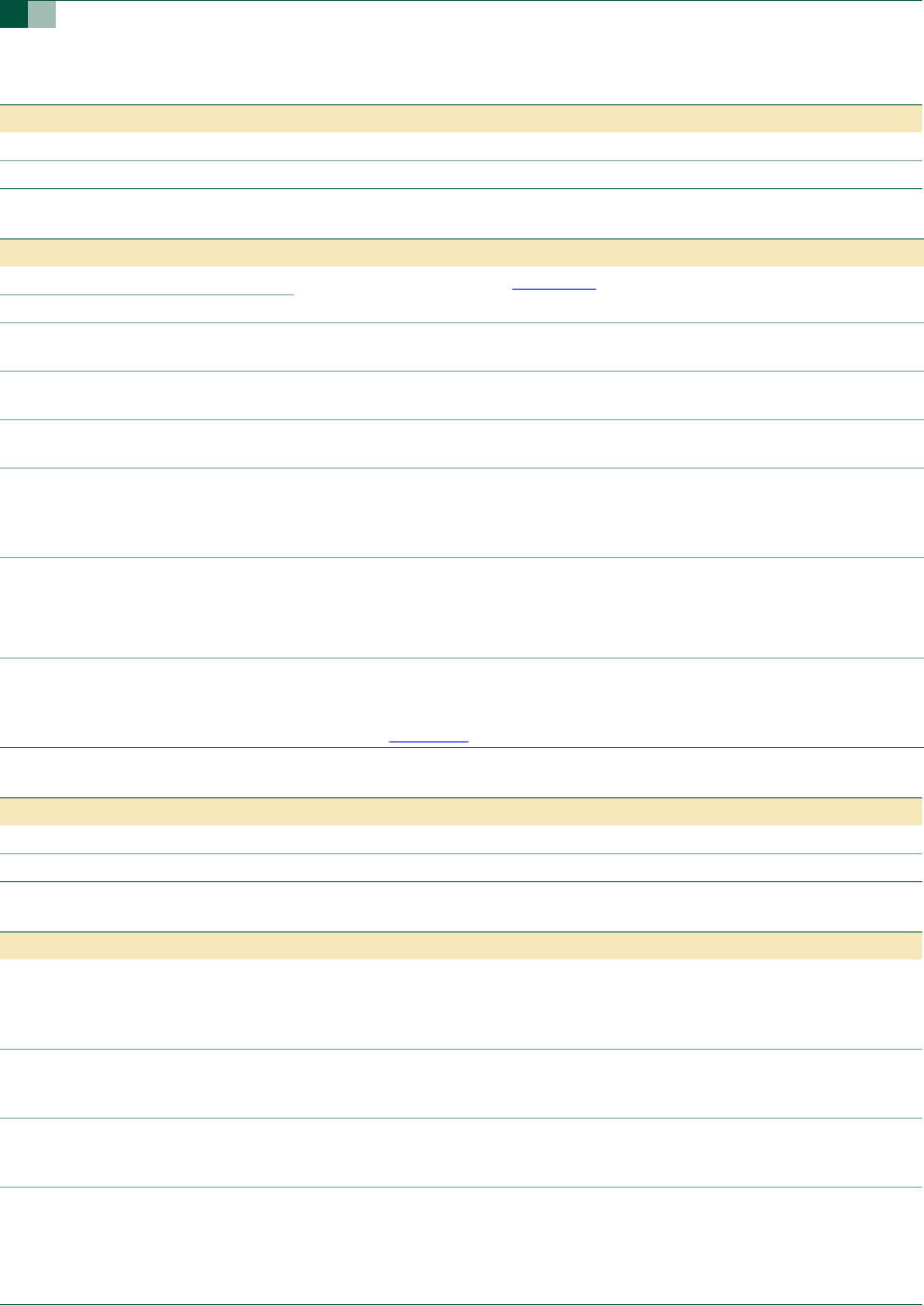

Table 13: Power Control register (PCON - address 87h) bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol SMOD1 SMOD0 BOPD BOI GF1 GF0 PMOD1 PMOD0

Reset00000000

Table 14: Power Control register (PCON - address 87h) bit description

Bit Symbol Description

0 PMOD0 Power Reduction Mode (see Section 5.3

)

1PMOD1

2 GF0 General Purpose Flag 0. May be read or written by user software, but has no effect

on operation

3 GF1 General Purpose Flag 1. May be read or written by user software, but has no effect

on operation

4 BOI Brownout Detect Interrupt Enable. When logic 1, Brownout Detection will generate a

interrupt. When logic 0, Brownout Detection will cause a reset

5 BOPD Brownout Detect power-down. When logic 1, Brownout Detect is powered down and

therefore disabled. When logic 0, Brownout Detect is enabled. (Note: BOPD must

be logic 0 before any programming or erasing commands can be issued. Otherwise

these commands will be aborted.)

6 SMOD0 Framing Error Location:

• When logic 0, bit 7 of SCON is accessed as SM0 for the UART.

• When logic 1, bit 7 of SCON is accessed as the framing error status (FE) for the

UART

7 SMOD1 Double Baud Rate bit for the serial port (UART) when Timer 1 is used as the baud

rate source. When logic 1, the Timer 1 overflow rate is supplied to the UART. When

logic 0, the Timer 1 overflow rate is divided by two before being supplied to the

UART. (See Section 10

)

Table 15: Power Control register A (PCONA - address B5h) bit allocation

Bit 7 6 5 4 3 2 1 0

Symbol RTCPD DEEPD VCPD - I2PD SPPD SPD CCUPD

Reset00000000

Table 16: Power Control register A (PCONA - address B5h) bit description

Bit Symbol Description

0 CCUPD Compare/Capture Unit (CCU) power-down: When logic 1, the internal clock to the

CCU is disabled. Note that in either Power-down mode or Total Power-down mode,

the CCU clock will be disabled regardless of this bit. (Note: This bit is overridden by

the CCUDIS bit in FCFG1. If CCUDIS = 1, CCU is powered down.)

1 SPD Serial Port (UART) power-down: When logic 1, the internal clock to the UART is

disabled. Note that in either Power-down mode or Total Power-down mode, the

UART clock will be disabled regardless of this bit.

2 SPPD SPI power-down: When logic 1, the internal clock to the SPI is disabled. Note that in

either Power-down mode or Total Power-down mode, the SPI clock will be disabled

regardless of this bit.

3I2PDI

2

C power-down: When logic 1, the internal clock to the I

2

C-bus is disabled. Note

that in either Power-down mode or Total Power-down mode, the I

2

C clock will be

disabled regardless of this bit.