© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

User manual Rev. 02 — 23 May 2005 23 of 133

Philips Semiconductors

UM10109

P89LPC932A1 User manual

level. When system power is removed V

DD

will fall below the minimum specified

operating voltage. When using an oscillator frequency above 12 MHz, in some

applications, an external brownout detect circuit may be required to hold the device

in reset when VDD falls below the minimum specified operating voltage.

2.7 Oscillator Clock (OSCCLK) wake-up delay

The P89LPC932A1 has an internal wake-up timer that delays the clock until it stabilizes

depending to the clock source used. If the clock source is any of the three crystal

selections, the delay is 992 OSCCLK cycles plus 60 µs to 100 µs. If the clock source is

either the internal RC oscillator or the Watchdog oscillator, the delay is 224 OSCCLK

cycles plus 60 µs to 100 µs.

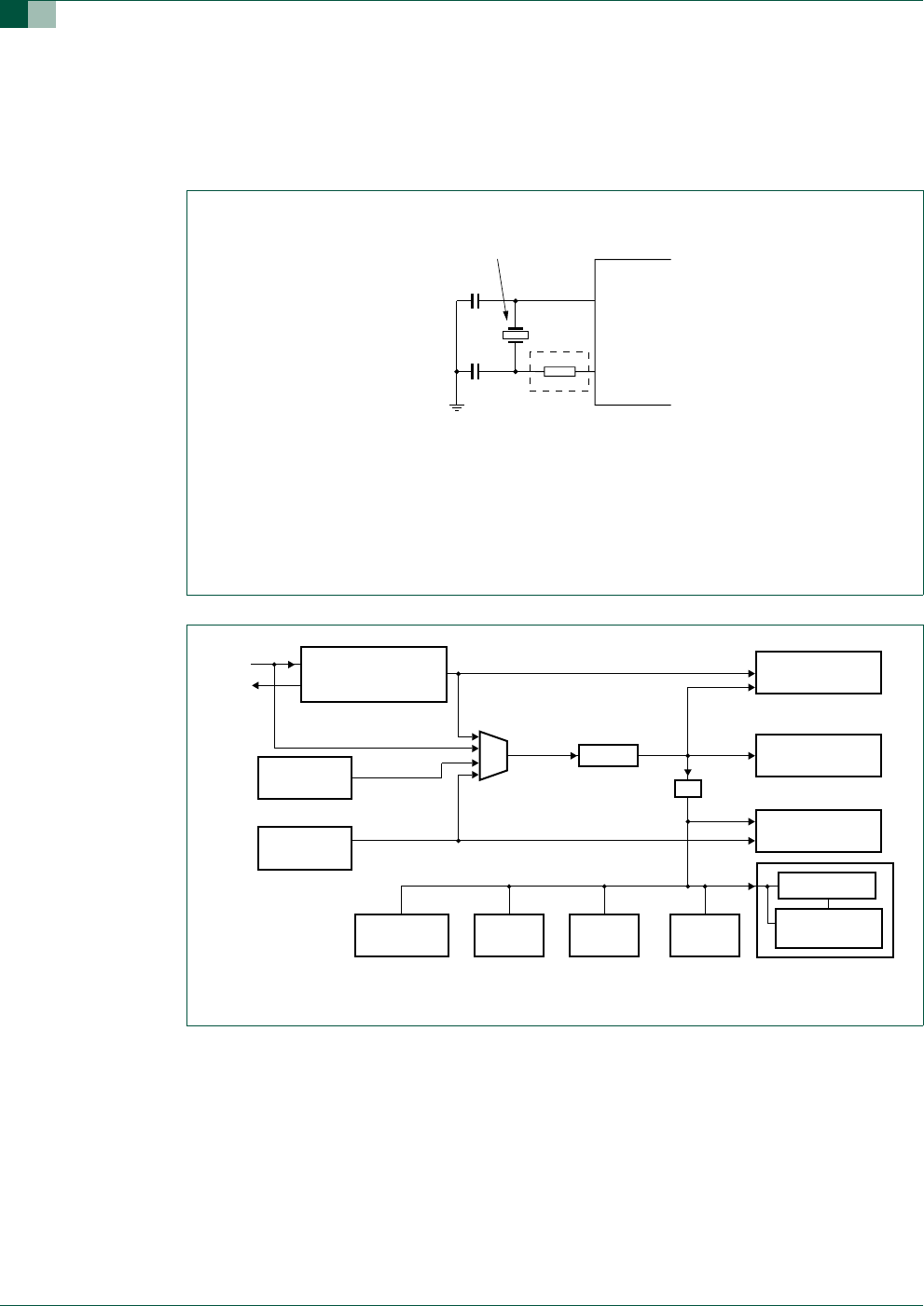

Note: The oscillator must be configured in one of the following modes: Low frequency crystal,

medium frequency crystal, or high frequency crystal.

(1) A series resistor may be required to limit crystal drive levels. This is especially important for low

frequency crystals (see text).

Fig 6. Using the crystal oscillator.

Fig 7. Block diagram of oscillator control.

002aab008

P89LPC932A1

XTAL1

XTAL2

quartz crystal or

ceramic resonator

(1)

÷2

002aaa891

RTC

CPU

WDT

DIVM

CCLK

UART

OSCCLK

I

2

C-BUS

PCLK

TIMER 0 AND

TIMER 1

HIGH FREQUENCY

MEDIUM FREQUENCY

LOW FREQUENCY

XTAL1

XTAL2

RC

OSCILLATOR

WATCHDOG

OSCILLATOR

(7.3728 MHz ±1 %)

PCLK

RCCLK

SPI

CCU

(P89LPC932A1)

32 × PLL

+20 %

−30 %

(400 kHz )