© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

User manual Rev. 02 — 23 May 2005 120 of 133

Philips Semiconductors

UM10109

P89LPC932A1 User manual

If the Configuration Write Protect bit (CWP) in BOOTSTAT.6 is a logic 1, writes to the

configuration bytes are disabled. If the Configuration Write Protect bit (CWP) is a logic 0,

writes to the configuration bytes are enabled. The CWP bit is set by programming the

BOOTSTAT register. This bit is cleared by using the Clear Configuration Protection (CCP)

command in IAP or ISP.

The Clear Configuration Protection command can be disabled in ISP or IAP mode by

programming the Disable Clear Configuration Protection bit (DCCP) in BOOTSTAT.7 to a

logic 1. When DCCP is set, the CCP command may still be used in ICP or parallel

programming modes. This bit is cleared by writing the Clear Configuration Protection

(CCP) command in either ICP or parallel programming modes.

18.16 IAP error status

It is not possible to use the Flash memory as the source of program instructions while

programming or erasing this same Flash memory. During an IAP erase, program, or CRC

the CPU enters a program-idle state. The CPU will remain in this program-idle state until

the erase, program, or CRC cycle is completed. These cycles are self timed. When the

cycle is completed, code execution resumes. If an interrupt occurs during an erase,

programming or CRC cycle, the erase, programming, or CRC cycle will be aborted so that

the Flash memory can be used as the source of instructions to service the interrupt. An

IAP error condition will be flagged by setting the carry flag and status information

returned. The status information returned is shown in Table 98

. If the application permits

interrupts during erasing, programming, or CRC cycles, the user code should check the

carry flag after each erase, programming, or CRC operation to see if an error occurred. If

the operation was aborted, the user’s code will need to repeat the operation.

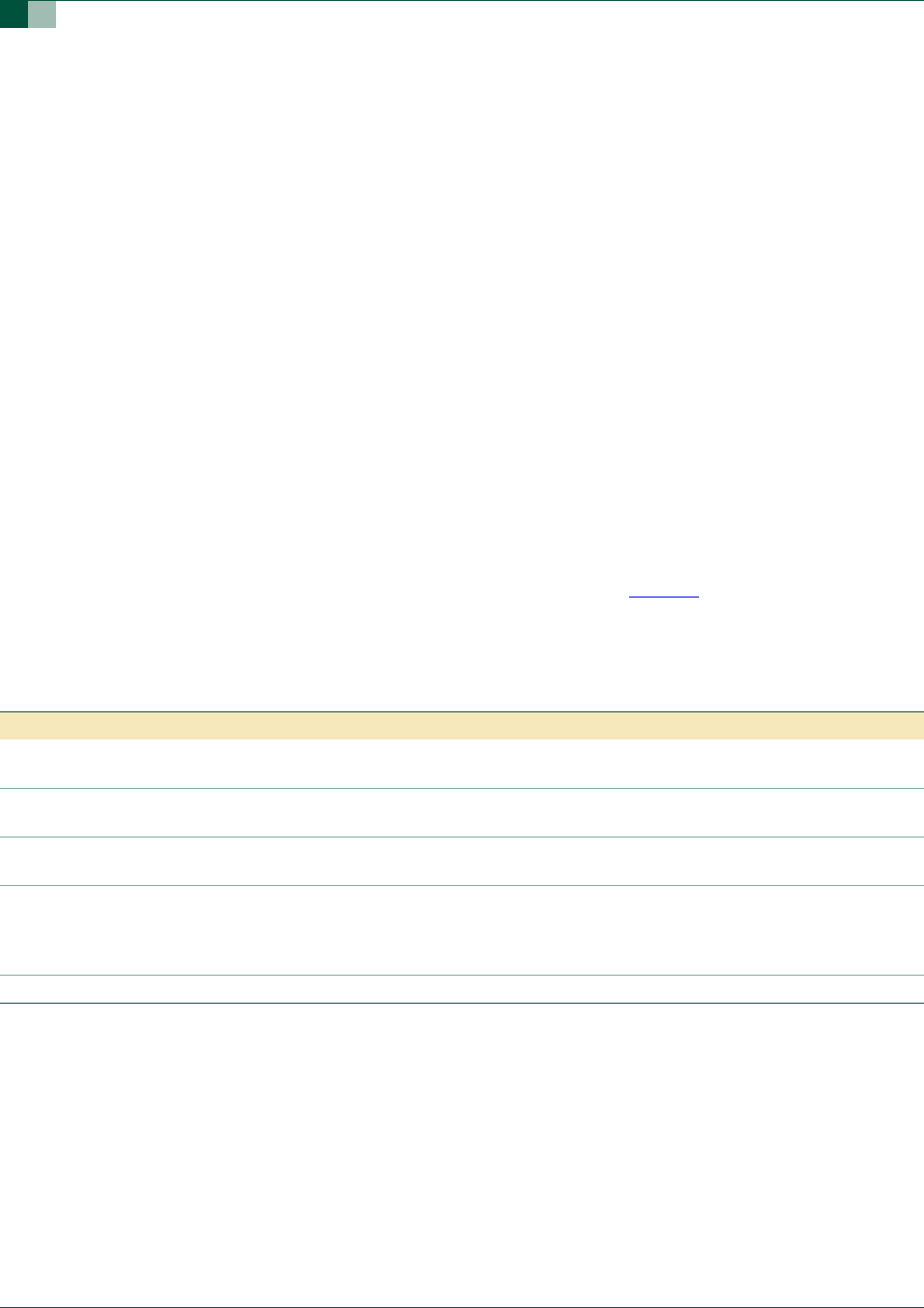

Table 98: IAP error status

Bit Flag Description

0 OI Operation Interrupted. Indicates that an operation was aborted due to an interrupt occurring during a

program or erase cycle.

1 SV Security Violation. Set if program or erase operation fails due to security settings. Cycle is aborted. Memory

contents are unchanged. CRC output is invalid.

2 HVE High Voltage Error. Set if error detected in high voltage generation circuits. Cycle is aborted. Memory

contents may be corrupted.

3 VE Verify error. Set during IAP programming of user code if the contents of the programmed address does not

agree with the intended programmed value. IAP uses the MOVC instruction to perform this verify. Attempts

to program user code that is MOVC protected can be programmed but will generate this error after the

programming cycle has been completed.

4 to 7 - unused; reads as a logic 0