1 - 4

1. SUMMARY

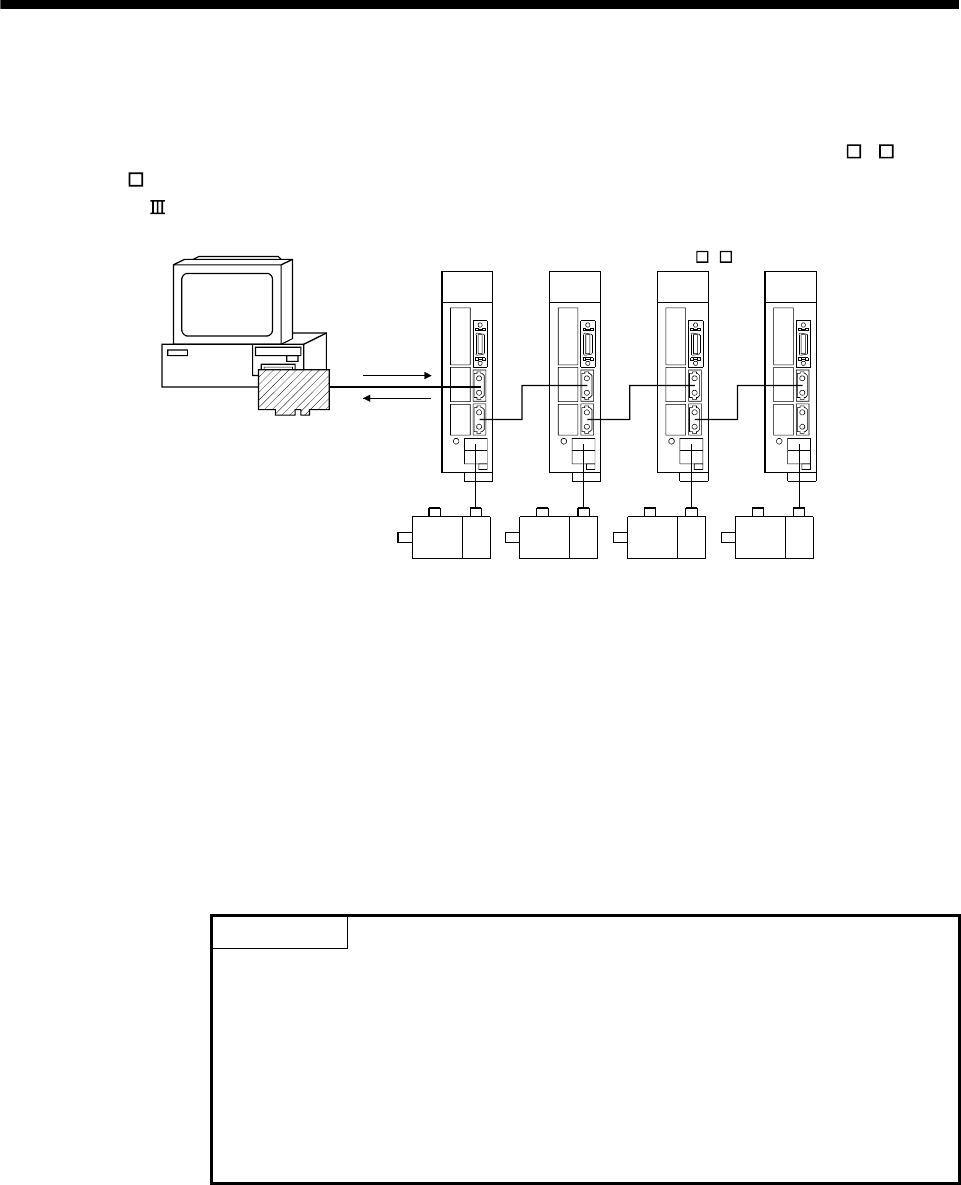

(2) PCI Express

®

bus compatible position board

The PCI Express

®

bus compatible position board (MR-MC240/MR-MC241) is a board compatible with PCI

Express

®

bus mounted to a PCI Express

®

system and controls our servo amplifiers (MR-J4(W )- B/

MR-J3(W)-

B). The PCI Express

®

bus compatible position board and the servo amplifiers are connected

with SSCNET

/H, which is a high speed synchronous network.

Position

instructions

parameters

Position

feedback

Speed

feedback

Host controller

Position

board

Servo amplifier (MR-J4(W )-

B)Servo amplifier (MR-J4(W )-

B)

For the PCI Express

®

bus compatible position board, there are two types, MR-MC240 and MR-MC241.

The MR-MC240 has one SSCNET control channel (hereinafter: CH) and one SSCNET communication line

(hereinafter: line), and can control positioning for up to 20 axes. The MR-MC241 has one SSCNET control

channel and two SSCNET communication lines, and can control positioning for up to 32 axes (up to 20

axes per communication line). Positioning is performed using a point table mapped on the dual port

memory of the PCI Express

®

bus compatible position board. Arbitrary positioning is possible by writing data

to this point table from the PCI bus compatible host controller.

Also, startup of JOG operation and home position return, etc. as well as parameter changing and

monitoring are possible through accessing this dual port memory on the position board from the host

controller. The dual port memory is mapped on the memory space of the PCI Express

®

bus.

POINT

• Depending on the specifications of the host controller, the PCI Express

®

slot

may be directly connected to the CPU of the host controller.

If the PCI Express

®

compatible

position board is mounted to a PCI Express

®

slot that is directly connected to the CPU of the host controller, it may not be

able to operate.

Mount the PCI Express

®

compatible

position board to a PCI Express

®

slot that

is not directly connected to the CPU of the host controller (connected to a

chipset).