5-7

STANDARD AND PTS INTERRUPTS

When the level-sensitive event is selected, the external interrupt signal must remain asserted for

at least 24 T

XTAL1

(24/F

XTAL1

) to be recognized as a valid interrupt. When the signal is asserted,

the level sampler samples the level of the signal three times during a 24 T

XTAL1

period. When a

valid level occurs, the level sampler generates a a single output pulse. The output pulse generates

the EXTINT interrupt request. The level-sensitive mode is useful in noisy environments, where

a noise spike might cause an unintentional interrupt request.

When an edge-triggered event is selected, the input must remain asserted for at least two T

XTAL1

(2/F

XTAL1

) to be recognized as a valid interrupt. When a valid transition occurs, the transition de-

tector generates a single output pulse. The output pulse generates the EXTINT interrupt request.

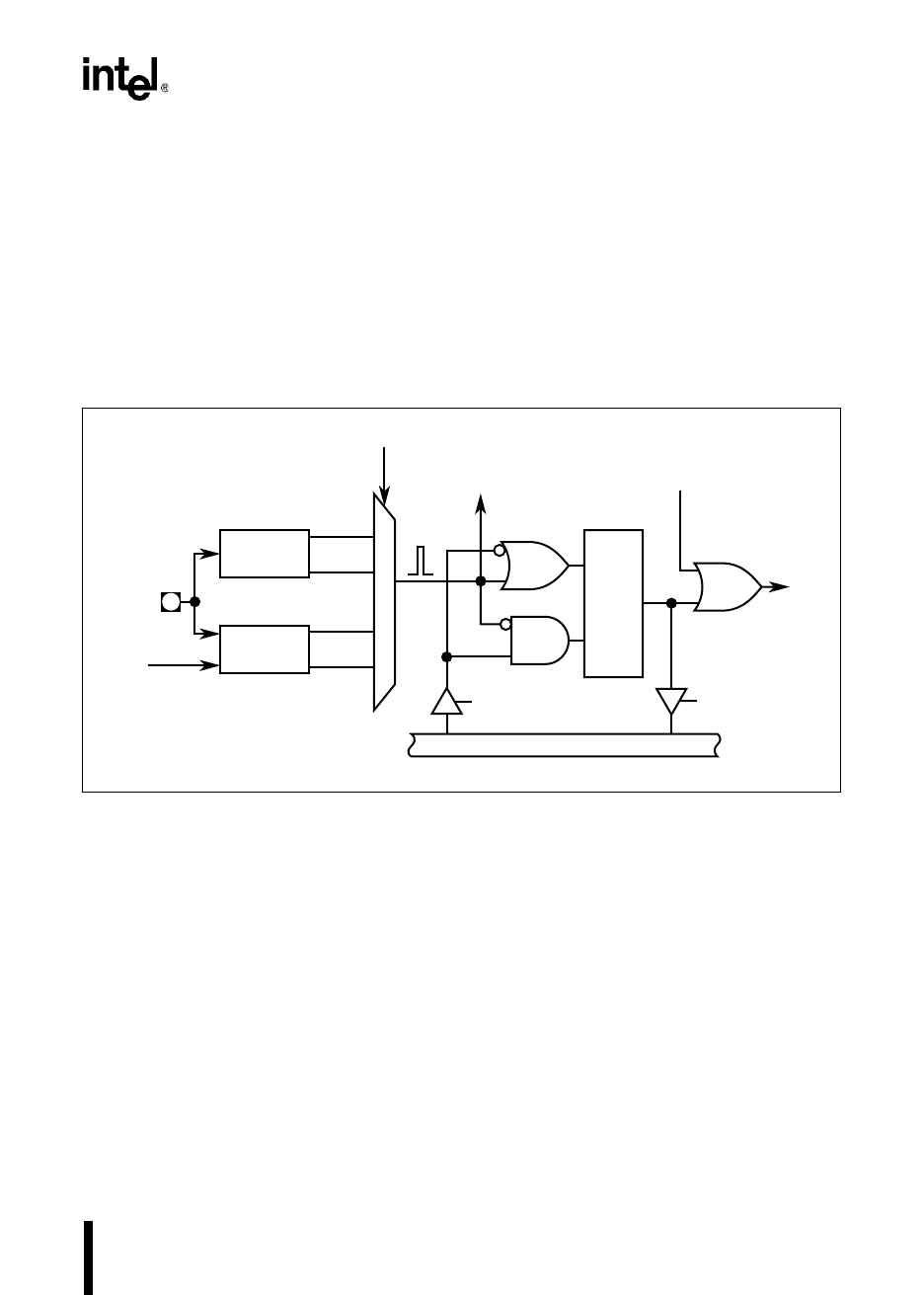

Figure 5-2. Waveform Generator Protection Circuitry

5.3.3 Multiplexed Interrupt Sources

The PI (MD), OVRTM (Mx), and SPI (MH) interrupts have multiple sources (see Table 5-3 on

page 5-5). An individual source will generate the interrupt only if software enables both the in-

terrupt source and multiplexed interrupt. To enable the multiplexed interrupt, set the appropriate

bit in the interrupt mask register (Figures 5-7 and 5-8). To enable an interrupt source, set the ap-

propriate bit in the PI_MASK register (Figure 5-9 on page 5-17). Figure 5-3 shows the flow for

the timer interrupt.

NOTE

Although the PI interrupt on the 8XC196MC has a single source (the

waveform generator), software must still enable both the source interrupt

(WG) in the PI_PEND register and the PI interrupt in the INT_MASK register.

A2661-01

EO Bit

Register

Transition

Detector

Q

Pulse

DP

R

S

00

01

10

11

Falling

Rising

Low

High

OD#

ES, IT

CPU Read EOCPU Write EO

CPU Bus

EXTINT

Interrupt

Request

Level

Sampler

EXTINT

F

XTAL1